Navigator Runtime 最大限度提高多内核效率

引言

多内核处理器给编程人员带来了新的挑战。在多内核项目中,半数以上的成本来自软件开发。多内核编程的具体挑战是非对称多内核处理器 (AMP),因为其中相同的器件中驻留着 RISC 与 DSP 内核等不同类型的处理单元。这主要是因为操作系统 (OS) 对资源管理与负载均衡的支持非常薄弱甚至根本没有,导致可扩展性差与资源利用率低。德州仪器 (TI) 创新型 KeyStone II 多内核架构提供专用硬件帮助实现调度与负载均衡功能,可简化多内核可编程性。KeyStone II通过这些措施实现了多内核编程的性能突破。

AMP 编程挑战

随着多内核技术的演进,越来越多的 SoC 提供对称多内核架构实现低成本以及更高的性能。典型的 AMP 具有运行在不同操作系统上的异构内核、硬件加速器以及非所有内核共享的分布式存储器。在对称多内核处理器 (SMP) 应用中,内核完全相同并运行支持相同共享存储器架构的相同操作系统,因此使用操作系统带来的内核间通信、调度以及负载均衡功能相对而言更为直接。AMP 器件的编程需要更高的并行编程技能,才能通过控制和协调不同的内核及操作系统实现可满足单内核或 SMP 编程需求的高稳定性及高性能。

传统非对称多内核处理要求在编译时对多内核资源进行静态分区。这样做难度往往较大,因为运行时的软件加载不能提前判别,尤其是 4G LTE、LTE Advanced 以及云计算等尖端技术。一般解决办法是预留额外的空间,以确保系统在最恶劣应用条件下也能正确运行。资源过度分配的不利影响是资源利用不足,最终会导致产品成本上升。另一方面,首次使用时或者引入新功能、需要现场强化或需求改更时,手动重新分区及软件优化会带来大量的软件工作。

同步性及处理器间通信 (IPC) 的效率在多内核编程过程中至关重要。缺乏对各种同步性与 IPC 机制的适当硬件支持,会因过多的软件开销而导致多内核利用低下,降低系统性能。

这对 AMP 多内核系统而言尤为如此,因为难以实现软件可扩展性与灵活性。

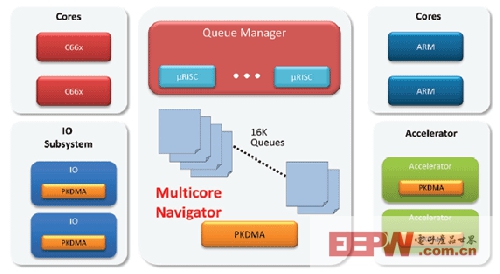

多内核导航器助力实现创新

多内核导航器是一种基于数据包的创新基础设施,支持数据传输与多内核控制。TI 异构 KeyStone 架构完美整合了 DSP Core-Pac、ARM? CorePac、硬件 AccelerationPac 以及 I/O 外设。它们不但可通过 TeraNet 进行物理互连,而且可通过多内核导航器进行逻辑互连。在 TI KeyStone II 架构中,多内核导航器不但包含可容纳 1.6 万个硬件队列的队列管理器,通常存放指向各种数据包(由描述符及数据有效负载组成)的指针,而且还包含 8 个 3,200 MIPS uRISC、用于传输数据的数据包 DMA 以及支持 100 万个描述符的硬件数据结构。此外,还可在 AccelerationPac 与 I/O 子系统中构建数据包 DMA,这样多内核导航器无需内核干预,便可将数据从任何单元传输至任何端点。

多内核导航器为 CorePac、AccelerationPac 以及 I/O 提供统一接口,可将硬件队列用于图 1 所示的不同系统端点。这可为所有 IP 块提供支持通用通信方式的 AMP 系统。多内核导航器可充分利用内建在队列管理器中的 uRISC 内核来管理流量路由、IPC、资源管理、调度以及负载均衡,从而可优化和加速数据流。各种任务可由队列管理器按需派送和分配给负载最轻的内核或 IP 子系统。

图 1:多内核导航器子系统

多内核导航器可提供高效率内核间通信机制。硬件队列与数据包 DMA 是 IPC 的基本构建块。某些队列经过精心设计,可对 IPC 内核产生中断。多内核导航器内部的 uRISC 内核使用可编程中断通知功能实现自动队列监控与管理。多内核导航器可充分限制软件开销,降低同步时延,并可提高 IPC 吞吐量。此外,它还支持无锁编程模型。图 2 是使用多内核导航器的 IPC 示意图。

图 2:使用多内核导航器实现处理器间的通信

Navigator Runtime 帮助您最大限度提高多内核效率

虽然采用 TI KeyStone II 硅芯片架构已经解决了多内核挑战,但只有应用软件开发人员充分发挥多内核性能,才能真正实现这种硬件架构的各种优势。在软件方面,TI 正在投资标准编程方法,让支持多内核导航器的 KeyStone II 的各项优势充分体现在应用中。行业中及学术界已经涌现出大量有望成为标准的多内核编程趋势。所有这些方法的共同之处在于应用软件开发人员先通过语言表达,采用特定手段描述其应用的并行性,然后再映射至底层运行时。该运行时可掌控将过程映射至底层硬件架构。

Navigator Runtime 是一个可扩展薄软件层,可帮助多内核导航器实现更高水平的并行编程性能,提高可扩展性、移植性及效率。对 AMP 编程挑战而言,多内核导航器和 Navigator Ru

NavigatorRuntime 多内核效率 KeyStoneAMP 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)