基于TPS54310的SOC电源电路设计

SYNC设置的固定频率误差为±20%,不符合SOC系统的高精度要求,因而选用频率可调的方式。

3.2 选择输入电容

TPS54310的输入端需要一个去耦电容(图3中的C9)和一个大电容(图3中的C1)。去耦电容用于降低器件输入端的高频噪声,选择陶瓷电容并尽量使之与芯片靠近放置以保证完全起作用;大电容用于降低输入总线的电压波动,如果选择的去耦电容足够大(10μF以上),能够进行足够的滤波,则大电容可以省略。决定是否需要大电容的因素有:

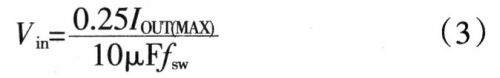

(1)系统输入电源允许的最大波动值(Vrip),为保证正常工作,Vrip却应该低于300mVpp,根据式(3)有

式中:Vin为没有大电容时的实际最大的峰峰波动电压值;IOUT(MAX)为最大的直流负载电流;fsw为选择的转换频率,如果Vin值大于Vrip的值,则需要大电容。

(2)如果加了一个大电容,该电容能够降低在高端场效应管启动时间内产生的电流脉冲所带来的输入电压的变化,而流经大电容的匹配电阻(ESR)的电压也会带来波动,因而要求使用大电容和小匹配电阻。

3.3 选择输出滤波器组件

输出滤波器组件包括输出电感(图3中的L1)和输出电容(图3中的C2)。选择输出电容需要考虑三个因素:直流额定电压、额定的波动电流和最大的输出波动电压,其直流额定电压至少大于输出电压的10%。

3.4 选择补偿组件

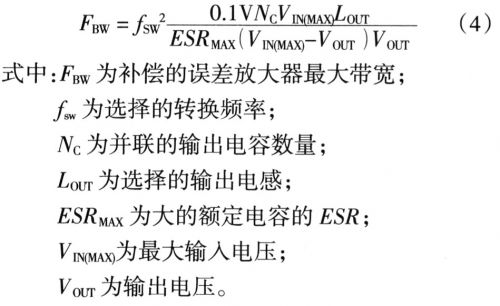

如图3所示,C7、R3、C6和R5、R1、C8共同构成电路补偿回路网络。当设计补偿时,需要考虑很多因素,首先,根据式(4)检测补偿的误差放大器允许的最大带宽,设计时应该使实际的带宽小于FRW。

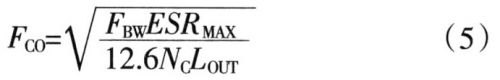

然后,根据式(5)计算所需的的回路交叉频率FCO,FBW的值由式(4)得出。

式中:FCO为所需的回路交叉频率;LOUT为选择的输出电感。

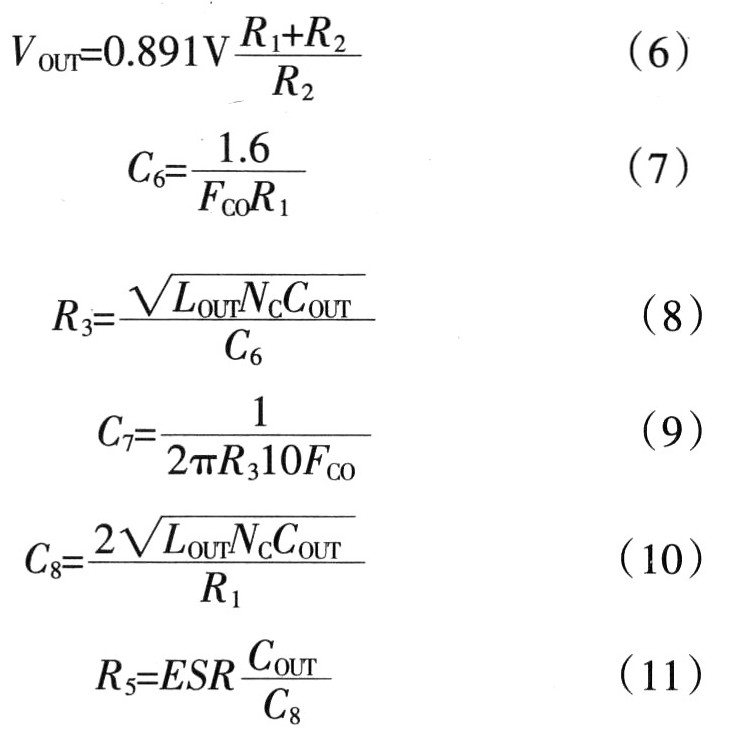

最后计算R2,C7、R3、C6和R5、R1、C8的值。首先选择R1和R2的值,这两个电阻值决定了输出电压的值,因而必须是0.1%精度电阻。R1的范围在10kΩ到50kΩ之间,然后根据式(6)计算出指定输出的电压值,再确定R2的值。然后利用式(7)一式(11)选择C7、R3、C6和R5、C8的值。

3.5 选择慢启动时间

由式(1)可知,在SS/ENA管脚上连接的电容使启动延迟了16ms。

如图3所示,Vin为输入端,Vo为输出端;R2用于决定输出电压的值;100μF的C1和47μF的C9共同构成了输入信号的去耦合器;C7、R3、C6和R5、R1、C8共同构成电路补偿回路网络;L1和C2作为输出信号的滤波器;RT引脚接了一个178kΩ的电阻而SYNC悬空,即内部的转换频率在280kHz到700kHz之间可调,由式(2)可得,

另外,在实际设计中,为了保证输入信号的噪声尽可能小,还应该在电源与输入引脚之间连接一个LC滤波器。

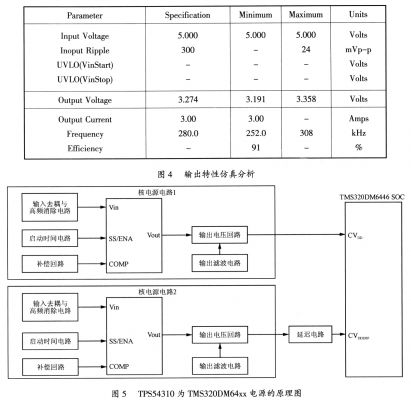

对芯片的输出特性进行了软件仿真分析,如图4所示,当设定输入电压为5V,输出电压为3.3V,转换频率为280kHz时,其实际输出电压在3.191V到3.358V之间,最大误差为3.3%,具有较高的精度和稳定度;输出电流为3A,具有较强的驱动能力;实际的转换频率在252kHz到300kHz之间,满足系统对电源响应速度的要求;功耗与效率相关,效率越高,在负载功耗一定的情况下,系统总功耗就越低,芯片的最低效率达到91%,完全满足系统的低功耗要求。由上述分析可知,该电路工作性能良好。

1.2V电源电路和1.8VI/O电路的产生方法与上述方法相同。通过核电源与I/O电源产生电路之间加入延迟电路来保证上电时序的正确性。图5显示的就是以TPS54310为基本核心的多组电路TMS320DM64xx电源的原理图。

4 结语

以高性能DC/DC调节器TPS54310为核心设计的TMS320DM64xx SOC电源电路,能够提供稳定精准的核电压和I/O电压,外部附加简单的延时电路可以保证正确的上电时序,能够为SOC系统建立可靠的电源电路,正确实现SOC系统的功能。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)