基于DSP的全桥移相控制感应加热电源研究及应用

0 引言

随着感应加热电源对自动化控制程度及可靠性要求的提高,感应加热电源正向智能化与数字化控制的方向发展。DSP具有高速的数字处理能力及丰富的外设功能,使得一些先进的控制策略能够应用实践,研究基于DSP的数字控制感应加热电源,可使产品具有更加优良的稳定性及控制的实时性,并且具有简单灵活的特点。本文以TMS320F2812为核心,设计了超音频串联谐振式感应加热电源的数字化控制系统,包括数字锁相环(DPLL)、移相PWM发生与系统闭环控制等。

1 系统结构

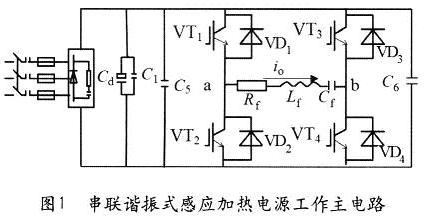

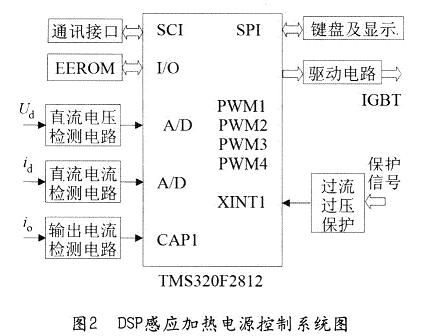

串联谐振式感应加热电源主电路如图1所示。采用不控整流加可控逆变电源结构,负载为感应线圈(等效为电感)与补偿电容串联。逆变部分采用带锁相环的移相PWM控制。基于TMS320F2812的系统控制框图如图2所示。其中直流侧电压检测电路和电流检测电路用于系统的闭环控制;输出电流检测电路是获取负载电流频率脉冲信号,用于频率跟踪的同步信号。

2 移相PWM调功原理

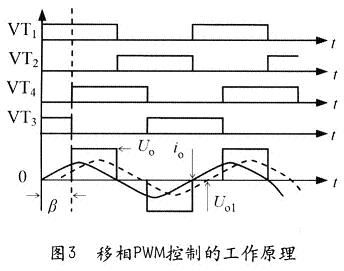

图1中由VTl和VT2的臂作为基准臂,VT3和VT4的臂作为移相臂,控制脉冲如图3所示。由图可见,其中VT1和VT2、VT3和VT4控制信号仍然保持互补相位关系,但VT3和VT4控制信号分别滞后VT1和VT2角度β,该角度在0~π范围内连续可调。改变移相臂的相位角β即可改变输出电压波形,从而改变电压基波有效值,实现桥内调压的目的。

设输入直流电压为Ud,VT4控制信号滞后VT1控制信号β角。则电路输出功率可用基波有功功率表示:

3 基于DSP控制系统的实现

1)数字锁相环与移相PWM信号的发生

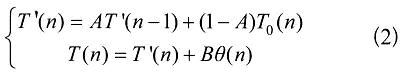

采用TMS320F2812的EV单元,结合数字锁相环基本算式,可有效实现感应加热电源的频率跟踪。数字锁相环基本算式如下:

式中,T0(n)为同步信号周期,T1(n)为二阶滤波后的结果,T(n)为频率相位修正后的结果。A为频率修正系数,B为相位修正系数。

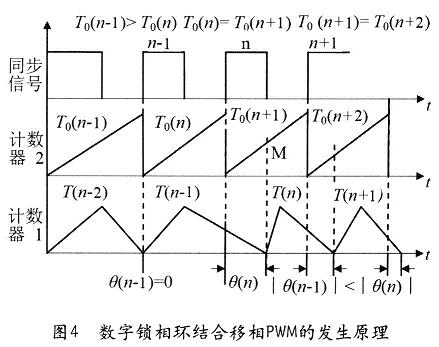

基于TMS320F28l2实现数字锁相环(DPLL)的基本原理如图4所示。算法过程如下:

(1)设置捕获单元为上升沿捕获,当同步信号脉冲的上升沿到达到,计数器2从零开始计数,当下一个脉冲上升沿到达时,捕获计数器2的值,得到同步信号的周期值T0(n)。

(2)开放定时器1的下溢中断,当计数器l为零时即进入下溢中断,立即读取并记录此刻计数器2的值,如图4中点M,该值即为相位差θ(n),将其存入到相应寄存器中,等待程序调用。

(3)调用相关变量,基于锁相环基本算式,计算得到新的周期值T(n)。

(4)判断T(n)是否在频率限定范围之内,限幅处理后,将T(n)作为计数器1下一周期的周期值,这样在每个周期都进行调节便可实现锁相的目的。

考虑到移相PWM信号的发生,这里需设置计数器l为连续增减计数模式,所以实际载入周期寄存器的值的需再除以2。

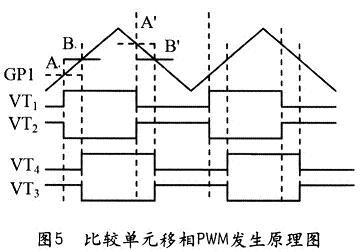

移相PWM信号的发生原理如图5所示。设置定时/计数器1(GPl)为连续增减计数模式,设A和A′两点对应于比较单元l(CMPl),B和B′对应于比较单元2(CMP2)。比较单元1与比较单元2分别输出两路互补的脉冲信号。在GPl的下溢中断和周期匹配中断及时改变定时器比较寄存器的值,即可产生所需的移相PWM信号。

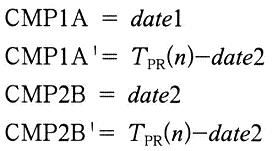

比较寄存器值的算法如下:

其中,TPR(n)为定时器l的周期值,date1和date2为两个变量值。改变datel与date2的差值,即可得到移相角可控的PWM输出。

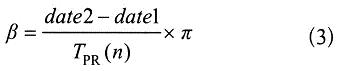

设移相臂的滞后角度为β,则

由式(3)可知,当datel=0,date2=TPR(n)时,移相角β最大,此时移相范围为0~π,但在DSP的程序设计中datel(A点)是不能取零的,所以在这种算法下,移相角的范围与datel的最小取值有关。

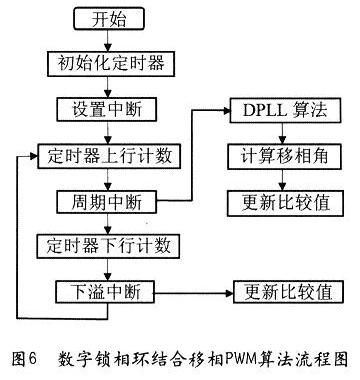

结合数字锁相环与移相PWM的发生原理,可以设计出两者相结合的算法,在DSP中的算法流程图如图6所示。

2)闭环控制

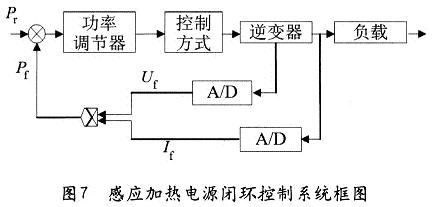

本文采用闭环控制结构如图7所示。检测输出电压及电流变化,将反馈信号输入到DSP的ADC采样端口,进行模数转换,得到电压与电流的反馈值,然后通过乘法器将两者相乘,再与给定比较,功率调节器的输出控制逆变器的移相角度,使输出功率保持恒定。

因为感应加热电源系统负载的惯性比较大,即参数变化比较慢。因此,可以不考虑PID微分环节,采用PI调节,就可以满足系统的控制要求。

3)相位补偿与启动问题

由于系统在实际运行中硬件滞后的影响或是程序执行效率的影响,在没有进行相位补偿的时候,控制信号必滞后于反馈信号某一角度。在实际应用中常采用外部相位补偿电路实现输出与反馈的相位同步,同样也可以在程序中进行补偿。本文在锁相环的算法程序中添加了相位补偿环节。在相位差的计算中引入误差角θerr,令

式中θ′(n)为重新计算后的相位差,将其作为DPLL算法中的相位差即可实现输出脉冲的相位补偿。根据实验测试与

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)