基于DSP的16通道声发射同步数据采集电路设计

3 数据采集电路的底层软件实现

数据采集电路的底层软件实现包括配置和数据采集两部分。其中,配置又可分为两部分:一是对VC5509A本身的初始化,包括:CSL库、PLL、GPIO、I2C、定时器、McBSP、DMA和中断等:二是对ADS1278参数的设置,包括通道开启情况、工作模式和采样率等。数据采集工作主要是由DMA来完成的,CPU只负责切换缓冲区和处理数据等操作。

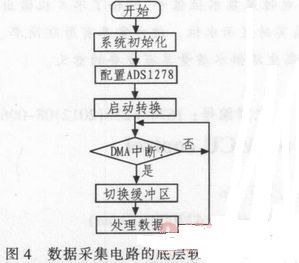

数据采集电路的底层软件工作流程如图4所示。系统上电后,首先完成初始化和ADS1278的配置工作;然后,CPU发出同步转换脉冲,启动数据转换,进入中断等待状态;与此同时由DMA来进行数据采集,当DMA存满缓冲区后触发中断;CPU进行切换缓冲区和数据处理等操作,然后返回等待下一次中断。

在上述过程中,DMA和CPU是并行工作的:即DMA专门负责存储数据,将数据搬移到缓冲区:而CPU则负责切换缓冲区并处理缓冲区内的数据。但同一时刻,CPU和DMA操作的是不同的缓冲区:当DMA向缓冲区0存储数据时,CPU处理缓冲区1的数据:而DMA向缓冲区1存储数据时,CPU处理缓冲区0的数据。这样DMA和CPU实现了一种"乒乓"切换操作,使得DSP能够更加专注于数据处理,从而能够发挥最佳性能。

4 数据采集测试结果

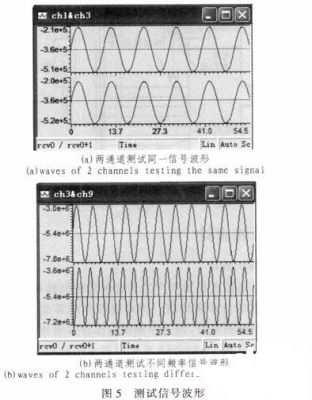

由于数据采集电路的通道数众多,无法一一展示测试结果,所以本文选取了两组典型通道,分别测试同一信号和不同频率的信号。用CCS集成开发环境进行硬件仿真,在DMA中断里设置断点,并通过Graph工具调取缓冲区内的数据显示采集信号波形,结果分别见图5(a)、(b)所示。测试中,设置ADS1278的采样频率为9 375 Hz,显示缓冲区大小为1 024个点,图中的横坐标是经换算过后的时间信息,单位是ms,纵坐标是A/D转换后的实际数值。

图5(a)中的测试信号频率为100 Hz,幅值为100 mVpp。由图可以看出,两通道采集的信号波形一致,相位相同,说明了两通道采样的同步性。图5(b)中,通道3信号频率为200 Hz,幅值约为1.45 Vpp;通道9信号频率为300 Hz,幅值为1.1Vpp。根据图中数据可以计算出,通道9的信号频率约为通道3的1.5倍,信号幅值约为通道3的1.3倍,与测试信号对应,这说明了两通道采集不同信号的正确性。图5(a)和(b)两图中的信号连续光滑,没有突变点,这也说明了采集电路的高性能。

5 结论

文中面向煤岩声发射信号采集,提出了一种大动态范围、多通道同步数据采集电路的解决方案。该方案通过较少的接口既实现了多通道数据的同步采集,又可灵活开启各通道、设置工作模式和采样率等。采用本数据采集电路的方案,还可方便增加ADS1278到8片,将通道数扩展到64个,进而实现更多通道数据的同步采集。但在使用时需注意,该数据采集电路可扩展的通道数会受到工作模式和工作时钟频率的制约。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)