基于S3C2440的嵌入式IPv6防火墙设计

在众多的网络安全设施中,防火墙是行之有效的重要网络安全设备,通过对网络通信进行筛选屏蔽以防未经授权的访问进出计算机网络。防火墙是位于可信网络和不可信网络之间的一道安全屏障,其最核心的任务就是管理和控制进出网络的通信量,它可以截获中途传输的数据包并进行处理,然后与事先定义好的安全策略规则相比较,并最终决定转发或丢弃该数据包。传统的防火墙通常位于一段网络的边界,它可以很好的过滤外界用户对内部网络的访问,但对内部网络的攻击却无能为力。针对此问题近年来关于新型防火墙的研究有很多,如分布式防火墙系统,嵌入式防火墙系统等。这些系统的目的是将防火墙的边界延伸,使其能够遍布网络的每一个终端设备,构建全方位的安全防护网络。

现有防火墙系统大多是针对于IPv4开发的,由于IPv4地址空间不足,且安全性较差,现有网络升级到IPv6是大势所趋。IPv6 作为下一代网络的基础以其海量的地址空间和较强的安全特性得到广泛的认可,因此研究支持IPv6协议的防火墙是很有必要的。

以Intel Xscale IXP425 为核心处理器设计的嵌入式IPv6 防火墙,较好的实现了对网络中的数据包进行动态过滤。但其成本较高,且IXP425 强劲的网络处理性能在网络终端的应用中无法得以完全发挥。

基于U盘的嵌入式防火墙使用方便,设计新颖,但其需要依附于x86 电脑硬件平台,且U盘的可靠性较差,不适于长期使用。

通用ARM 处理器有较高的性价比和较多的软件支持,已广泛应用于生产生活的各个领域。本文通过对IPv6协议、IPv6安全机制和防火墙技术等方面的分析和研究,结合现有防火墙的特点,设计并实现了一个基于S3C2440 的嵌入式IPv6 防火墙系统。下面从硬件设计、软件设计和核心模块设计几个方面介绍该基于S3C2440的嵌入式IPv6防火墙。

2 嵌入式IPv6防火墙的硬件设计

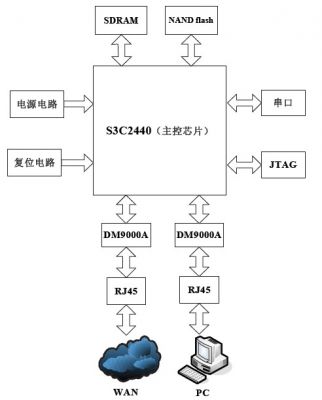

嵌入式IPv6防火墙的硬件设计如图1所示,其主控芯片采用三星公司的32 位嵌入式处理器S3C2440.该处理器以ARM920T RISC 为核心,标准工作频率为400MHZ(最高工作频率:533MHZ),运算能力为450MIPS,有强劲的处理能力。

图1 嵌入式IPv6防火墙硬件框图

S3C2440处理器内部结构复杂,功能强大,片上集成了很多硬件资源。如:外部存储控制器,USB 接口,UART接口,内部定时器,130 个通用I/O接口,24 通道外部中断源等。如此丰富的接口资源,可以很方便实现硬件电路的扩展。此外S3C2440 支持ARM920T 强大的指令集系统,具有独立的内存管理单元(MMU),支持NAND Flash启动引导,可以方便的实现Bootloader和嵌入式操作系统的移植。

系统的存储单元主要包括SDRAM 存储器和Flash存储器。SDRAM为系统程序的运行提供内存空间,本系统采用两片HY57V561620FTP-H(32M)并联,容量可达64MB.Flash用来存储程序,Flash分为NOR型和NAND型2种。NOR型Flash工艺复杂,成本较高,其优点是片内可执行应用程序,多用于存储系统的Bootloader 引导程序。NAND 型Flash 具有极高的存储密度和较快的写入和擦除速度且成本较低,适用于存储大容量数据和文件。考虑到S3C2440支持NAND Flash 启动引导,故本系统选用K9F1208U0M-YCB0(64MB)的NAND型Flash作为系统的Flash存储器。

系统的以太网接口单元采用2 颗10M/100M 自适应以太网控制器DM9000A.DM9000A 芯片是DEVICOM 公司研发的一款低功耗,高度集成,成本较低的单芯片快速以太网芯片,在嵌入式领域中使用非常广泛。它集成了物理层接口(PHY)、以太网媒体介质访问控制器(MAC)和外部处理器总线接口等。3.3V的工作电压,降低了系统的功耗。DM9000A 的高度集成简化了系统以太网电路的硬件设计,特别适合作为嵌入式IPv6防火墙的网络接口。

3 嵌入式IPv6防火墙的软件设计

嵌入式IPv6 防火墙系统的软件编写采用了模块化程序设计的方法。模块化编程有利于程序设计任务的划分,使程序易于编写和调试,便于检验和维护。

本系统将启动代码(Bootloader),Linux 操作系统(网卡驱动、协议栈),防火墙模块(智能包过滤,状态跟踪等)和WEB管理模块(Boa服务器)都编写成独立模块。

系统软件层次结构如图2所示。

图2 嵌入式IPv6防火墙软件层次结构图。

第一层:启动代码(Bootloader)。它是芯片复位后进入操作系统之前执行的一

- 嵌入式Web服务器移植与测试(03-03)

- 基于OpenWrt的移动机器人系统设计(01-17)

- 基于S3C2440处理器Linux平台的物流配送系统设计(02-05)

- 基于嵌入式的杯突试验机测控系统设计与实现(02-12)

- 基于ARM的多路同步的A/D和D/A设计(06-29)

- S3C2440模拟IIC方式操作EEPROM(12-03)