����HPI��ʽ�Ծ���TMS320VC5402 DSPоƬ��ʵ��

��һ���飬���ַֿ����ȹ̶��������DSP��Ԥ���Ļ������Ĵ�С�����㡣Intel��ʽ��HEX�ļ��ĸ�ʽΪ��BYTE1��Ϊÿ�����ʼ��־������"��"��BYTE2-3��ʾ�ÿ�����Ч���ݵij��ȣ��Ϊ32��BYTE��������Ч���ݿ����dz�����룬Ҳ��������չ��ַ��Ϣ��BYTE4-7��ʾ�ÿ��ڴ������ʼ��ַ��BYTE8-9�����ͣ�00��ʾ������룬01��ʾ������04��ʾ��չ��ַ��Ϣ��BYTE10֮���Ǵ��룬ֱ���������BYTE����ʾУ��λ��У��λ��ֵ�Ǹÿ�����ǰ����ֵ�͵IJ��롣

����ѡ����HEX��ʽ��CPU���Ȱ��ոø�ʽ�Ķ����Kernel��HEX���ݽ��н��ͣ���ȡ������Ϣ��CPU������TMS320VC5402Ƭ��RAM����ɿ�ִ��DSP����Ȼ����CPU��kernel�Ĺ�ͬ�����£���DSPӦ�ó����HEX���ݽ��н��ͣ�����������DSP�е�ƴ�ӡ���λ������DSPӦ�ó���--��ת��DSPӦ�ó������ʼ��ַ��

4 ϵͳ��Ӳ�������ʵ��

4.1 ϵͳ��ͼ

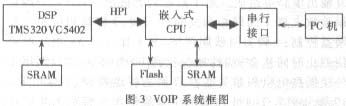

�ڱ��߿�����VOIPϵͳ�У�ʹ����HPI��DSP (TMS320VC5402)�����ԾٵĹ��ܡ�������Ӧ���ֵĿ�ͼ��ͼ3��ʾ��

����PC���忨��ϵͳ���ÿ�ͼ������ʡ�Ե�HPI���ҵIJ��֣���ֱ��ʹ��PC����CPU��Ӳ����Ϊ��Ӧ�Ŀ��ƺ�ֻ���洢����������������ҪΪDSP�䱸RAM����ʹ���������С�

4.2 Kernel�������

����ǰ����˵��kernel���������������ͻ��TMS320VC5402 4KƬ��RAM�ռ����Ƶ��м�����书���Ǿ��ǰ��պ�HOST CPU��ij��Լ������ȡDSP����������Ӧ��ַ��Ϣ����DSP���ܹ����ʵ��Ĵ洢���ռ�(Ƭ�ں�Ƭ��)����DSP������롣���� Kernel�Ĺ��ܱȽ��٣�����������÷dz�С�����йؼ�������DSP������벿�ֵĴ������£�

������

��bss addr 1 ;���������Ŀ�ĵ�ַ

��bss length 1 ;������볤��

��bss codedata 20 ;���ճ�����뻺����

������

��text

START��

������

MOVE��

STM ��addr AR4 ����ȡ�������Ŀ�ĵ�ַ

LD AR4 A

STM ��codedata AR3 ��ȡ�������

MVDM ��length AR5 ��ȡ������볤��

NOP

MAR +AR5 ��-1��

RPT AR5 ��λ

WRITA AR3+

������

ENDLOAD��

B app_start ������

������

4.3 ��������

����ǰ����ϵͳ���ɣ����Ƚ�PC���ϵ��Ժõ�Kernel�����DSPӦ�ó���(һ��ΪCOFF��ʽ)ת����HEX�ļ�����ͨ�����ڽ���Щ�ļ���ŵ�CPU��Flash�У��ڴ�Ź�����Ӧ��HEX�ļ�ԭ�����棬�Ա����������е���Ϣ����ϵͳ������CPU��Flash�л�ȡKernel��HEX���ݣ�ͨ��HPI������TMS320VC5402����ϳ�Kernel���г���������Ȼ��CPU����Flash�л�ȡDSPӦ�ó����HEX���ݣ�ͨ��HPI����ֿ����TMS320VC5402�������Ѿ���ʼ���е�Kernel�����������DSP���ó������ȷ��λ�������������DSPӦ�ó���

��ʵ���з��֣���ȻHPI����Ƴ�����Ϊ�˺͵���8λ���ӿڽ������ݽ���������HPI�����Ĺ����ٶȷdz��ߡ�ͨ��HPI��ʽ����һ�β�С��130K��DSPӦ�ó����������Ҫ��ʱ�䲻����3���ӡ�

TIϵ��DSP�ṩ����˷ḻ��Ӧ�÷�ʽ�����ɸ�DSPϵͳ�����ߴ����˼���ķ��㡣

HPI TMS320VC5402 DSP ������£�

- DSP HPI����PC104���߽ӿڵ�FPGA���(04-14)

- CPLD��DSPϵͳ�е�Ӧ�����(04-11)

- ����DSP��HPI�ӿڵ���Ƶ���ݴ���ϵͳ���(03-01)

- FPGA��DSPЭͬ����ϵͳ���֮�� FPGA��DSP��ͨ�Žӿ����(06-05)

- PC/104������HPI��ͨ�ŵĽ������(12-21)

- TMS320C6727 DSP����������ʽ���(10-22)