TMS320C6727 DSP两种引导方式设计

摘要:文中详细描述了TMS320C6727DSP两种引导方式,并给出了在工程应用的实现方法。这两种方法都避免了在设计过程中使用外部程序存储芯片,节约了布线空间和设计成本。在引导过程中,主机能够验证写入DSP芯片的数据,提高了系统的可靠性。

TMS320C6727DSP是TI公司的浮点信号处理芯片,该芯片具有处理速度快,运算精度高的特点,因此被广泛的使用。对该芯片进行应用程序加载通常采用的Parallel Flash方式,该方式需要一片外部存储芯片,加载程序相对复杂,在加载的过程中具有不可预知性。对于具有上位主机的系统来说,采用HPI或SPI0 SLAVE方式进行引导时,不仅不需要外部程序存储芯片,同时在引导的过程中可以严格的验证写入DSP芯片内的数据,具有更高的可靠性和灵活性。

1 引导方式配置

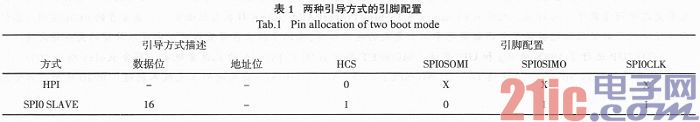

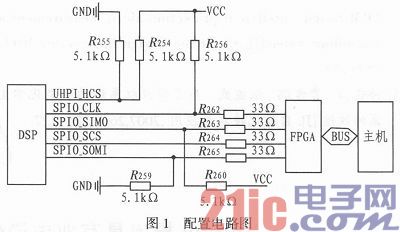

TMS320C6727(DSP)有HPI,SPI0,Parallel FLASH,I2C1等多种引导方式,不同的引导方式是通过芯片上电时读取外部引脚配置确定的,本文主要对HPI和SPI0 Slave两种引导方式进行详细介绍。引导方式的选择见表1,图1中描述了硬件实现方法。

根据图1,当选择HPI引导方式时,电阻R255焊接,断开电阻R254。当选择SPI0 SLAVE方式时断开电阻R255,同时焊接R254,R256,R259和R260。

2 SPI0 SLAVE方式

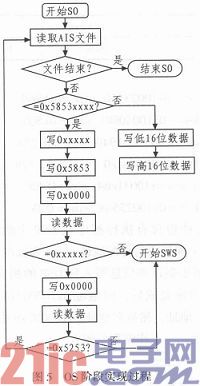

在芯片上电后通过确定BOOT引脚的配置来选择SPI0SLAVE引导方式,然后DSP运行固化在芯片内部的BOOTLOADER程序。DSP芯片的BOOTLO ADER引导程序主按照AIS通信协议与外部器件的通信,完成程序加载并运行。AIS协议的基本结构如图2所示。

AIS协议分为3个传输过程:SWS-POS-OS;具体描述如下:

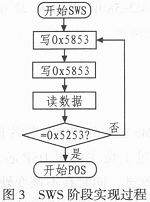

1)SWS阶段主要用来同步主机与DSP之间的通信连接,在这个过程中主机向DSP发送同步数据0x5853,同时主机进行接收,当主机接收到的数据位0x5253后,表示主机与DSP之间同步完成,并进行POS阶段。

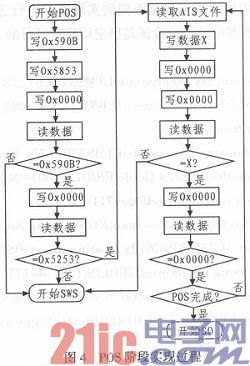

2)POS阶段主机首先发送数据0x5853590B,并收到从DSP发送的数据0x5852590B,然后主机向DSP发送一个数据N,在正确接收到数据N后,主机依次向DSP发送数据1-N,并收到相应的数据,在整个过程中,如果数据接收出错,则返回到SWS阶段。如果正确接收,则进入OS阶段。

3)OS阶段,主机首先向DSP发送一个AIS命令数据,所有的AIS命令数据都是以0x5853xxxx的格式组成的,当主机在向DSP发送命令数据时,主机会收到相应的返回数据,该数据的格式为0x5253xxxx。通过判断接收的数据可以在OS阶段监控数据的写入是否正常,当出现异常时,返回到SWS阶段,并从新开始正个过程。

3 HPI方式

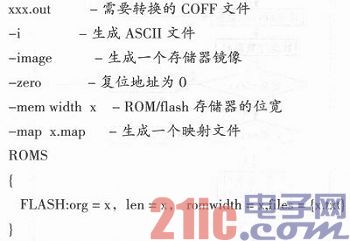

相对于SPI SLAVE方式,HPI加载方式则要简单的多,首先在DOS界面下利用HEX6X执行一个命令文件,把COFF文件转换成一个可下载的ASCII文件。命令文件的设置如下:

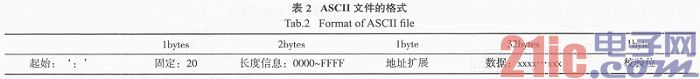

根据上面的命令文件,最终生成的ASCII文件每一行以‘:’开头,具体的格式如表2所示。

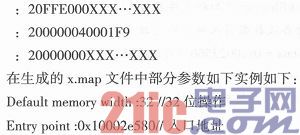

由表2可以看出,当COFF文件转换后的长度大于64kbytes时,长度信息将无法表示,为了避免产生这种情况,当数据长度大于64kbytes时,会自动增加一行,该行的主要功能是对地址进行线性扩展,在其下一行又从零开始,具体如下:

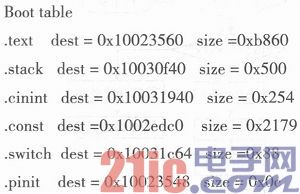

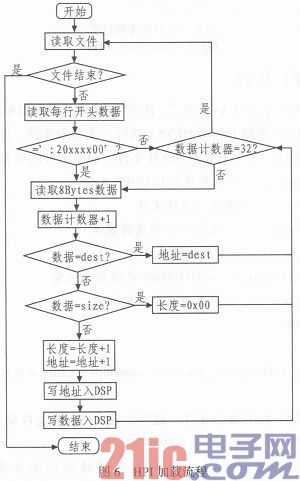

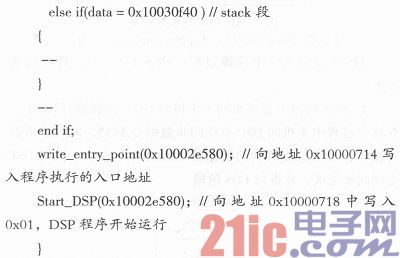

x.map文件包含有执行程序在DSP中的入口地址信息(entry point)和各段的分配地址(dest)和长度(size)信息。上电后,上位机根据这些信息写入到DSP的相应的地址,当整个文本文件传输完成后,向地址0x10000714中写入DSP程序执行的入口地址,然后向地址0x10000718中写入数据0x01使DSP开始运行。工作流程见图6。

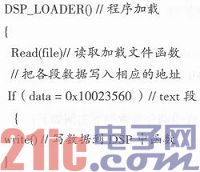

上位机实现加载的程序如下(C语言):

4 结束语

文中介绍了TMS320C6727DSP芯片的两种引导方式,这两种方式都是通过上位主机对DSP芯片加载应用程序,有利于DSP算法的改进,同时在不该变硬件的基础上能够通过简单的上位机程序就能对板卡进行扩展应用。这两种方法的上位机控制程序具有简单易懂和便于移植的特点。两种方法的区别在于,HPI方式由于是并行工作,因此速度很高,缺点是占用的引脚多,在硬件设计时对布线要求很高,而SPI0SLAVE方式以串行工作,相对来说程序加载时间相对较长,但是所需要的引脚很少,对于布线空间的要求低。在实际应用中该两种方式应根据不同的实际情况进行选择。以上两种方式在实践中已经被验证是稳定可靠并可行的。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)