����TMS320F206 DSP��ͼ��ɼ�����Ʒ���

�����źŴ�����DSP�������źŴ��������볬���ģ���ɵ�·VLSI�����ںϵĽᾧ��ĿǰDSP�������㷺��Ӧ����ͨ�š�������ͼ���캽�ա������DZ����������ƶ�������Ϣ�������ֻ�������������Խ��Խ������á�

�����õ绰�ߴ�����Ƶͼ����һ�ͱ����ʶ�ý��ͨ�������У����ѡ��ͼ������ר��оƬ����SAA7110��8��8 3104VCP�Լ�LSI��˾��ר��оƬ�ȣ�����ѡ�þ��и����������ܵĸߵ�DSP����ͼ����������ʹ��Ʒ�۸����ȱ��������Ľ��ܵIJ���TI��˾�ĵ͵�DSPоƬTMS320F206����ƵA/DоƬTLC5510��ͼ��ɼ�������Ϊ�ͱ����ʶ�ý��ͨ���ṩ��һ�����۵Ľ��������

1 TLC5510оƬ��TMS320F206оƬ���

1.1 TLC5510���

TLC5510��CMOS��8λ��20MSPSģ��/��ת����ADC���������˰�����semiflash architerture�ṹ��TLC5510�õ�5V��Դ���磬ֻ����100mW�Ĺ��ʡ��������ڲ������ͱ��ֵ�·������IJ�������Լ��ڲ������衣

������ת����flash converter��ȣ������ٽṹ�����˹�����ĺ�оƬ�ߴ硣ͨ����2������2-step-process��ʵ��ת�����ɴ����ٱȽ�������Ŀ��ת�����ݵĵȴ�ʱ��Ϊ2.5��ʱ�����ڡ�

�����ⲿ����ѹԴ�;��ܵ��裬��ʹ���ڲ��������VDDA�Ϳ�ʵ��2V��������ת����Χ��25��ʱ�����Զ����Ϊ±0.75LSB���������¶ȷ�Χ�ڵ����Զ�������ֵ��±1LSB��25��ʱ�IJ�����Զ����Ϊ±0.5LSB���������¶ȷ�Χ�ڵIJ�����Զ�������ֵ��±0.75LSB��

1.2 TMS320F206���

TMS320F206��TI��˾�Ƴ���һ��DSPоƬ�����ǻ���TMS320C5x֮�ϵĸ��ٶ������ִ���оƬ�����иĽ��Ĺ���ṹ���з���ij�����������ߡ�������CPU����Ч��ָ����ص㡣����Ҫ�������£�

CPU����32λCALU��32λ�ۼ�����16��16λ���г˷�����������λ�Ĵ������˸�16λ�����Ĵ�����

�洢������224K�ֿ�Ѱַ�洢�ռ䡢544��Ƭ��DRAM��4K��Ƭ��SRAM��32K��Ƭ�ڿ����洢����

ָ���ٶ�Ϊ50ns��35ns��25ns��ָ�����ڡ�

��Χ��·�������ɱ�̶�ʱ���������ɱ�̵ȴ�״̬��������Ƭ�����ʱ�ӷ�������ͬ�����첽ϵ�д��ڡ�

2 Ӳ���ӿڵ�·���

2.1 TLC5510ǰ�˵�·���

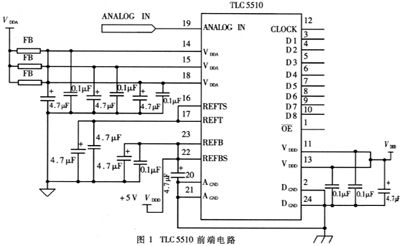

TLC5510ǰ�˵�·��ͼ1��ʾ��

�ڵ�·�У�ģ���ԴVDDA�����ֵ�ԴVDDD�������VDDA�����ֵ�AGND֮�估VDDD��ģ���DGND֮�䶼��4.7μ�Ƶ��ݡ�0.1μ�Ƶ��ݺ������Ż�ȥ���������Դ���Ʋ���AGND��DGND�ֿ����Ա��������źŸ�ģ���źŴ����������Ŵ�����Ƶ�ź�ֱ�Ӽ���TLC5510��19�š�TLC5510��ʱ���ź���TMS320F206��ʱ���ź������CLKOIU1�ṩ��

2.2 TLC5510 ��TMS320F206�ӿڵ�·���

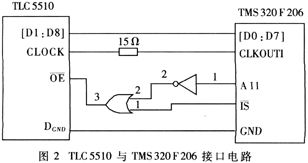

TLC5510��TMS320F206�ӿڵ�·ͼ��ͼ2��ʾ��

TLC5510���ֵ���TMS320F206�ĵ���������TLC5510�ڲ�������������壬����TLC5510�ĽŤ�D1��D8����TMS320F206�Ť�D0��D7��ֱ��������TMS320F206��CLKOUTI��ͨ��һС�����TLC5510�ṩʱ���źš�TMS320F206�ܽ�A11��Ϊ�����ƣ���A11Ϊ���ߣ�Ϊ����ʱ��TMS320F206�Ϳɴ�TLC5510��ȡ�������ݡ�

2.3 TMS320F206����������ͨ��

����TMS320F206��ͼ������ͨ��������9600 b/s��������������������������ݴ浽��������Ȼ��ͨ�����ص���ͼ��ת����������ʾ������ʾ������

3 �ӿڳ������

3.1�������ij�ʼ��

(1) ��������ݴ洢������ʼ��ַΪ0900h

(2) �������Ϊ1000h

(3) ��A/D��ַΪ0800h

3.2 ������

1 ��ʼ��TMS320F206

2 ���غ��ʵ�ARn

3 ѡͨTLC5510

4 ��ȡA/Dת��ֵ

5 ��ʼ��UART

6 ��UART ����

7 �������

3.3 �������

��title ″TLC5510 Interface″

��copy ″init.h″

��copy ″vector.h″

��text

ADC_Addr .set 0800h ������TLC5510�ĵ�ַ

Mem_pointer ��set 0900h �����ò������ݴ洢����

��ʼ��ַ

Count ��set 1000h ����������

start�� lar ar2��#ADC_Addr

lar ar3��#Mem_pointer

lar ar4��#Count

�� ��ʼA/Dת��

ldp #6h ������ҳ��ָ��ʹ��ָ��

50h��6=0300h��

splk #Count��0h ���Ѳ�����������0300h

Iar ar4��#0300h ��ʹAR4ָ��0300h

mar ����ar4 ����AR$��Ϊ��ǰ�Ĵ���

rpt ����ar3 ������RPTC�Ĵ�����

AR3��Ϊ��ǰ�Ĵ���

in ��+��ADC_Addr��ar4 �����벢�洢A/Dת��

���

��ͨ��UART��������������

����ʼ��UART��

clrc CNF ����B0��ӳ��Ϊ���ݿռ�

ldp #0h ������Ҷ��ָ��ʹ��ָ��0h��

setc INTM ����ֹ�����ж�

splk #0ffffh��ifr �����ж�

splk #0000h��60h

out 60h��wsgr ��������ȴ�

splk #0c180h��61h ���� UART�ڸ�λ

out 61h��aspcr ������I/O�ж�

splk #0e180h��61h

out 61h��aspcr ����I/O�Ͽ�

splk #4fffh��62h

out 62h��iosr ����ֹ�Զ�������

splk #00082h��63h

out 63h�� brd �����ò�����Ϊ9600

splk #20h��imr ������UART�ж�

lar ar3��#0900h ���ָ� AR3

lar ar4��# Count-1 ���ָ�AR4

mar ����ar3 ������ AR3Ϊ��ǰ�Ĵ���

clrc intm �����ж�

uart1�� setc xf ����xf��1����ʼ����

mar ����ar3 ����AR3��Ϊ��ǰ�Ĵ���

out ��+��adtr ���������ݺ�AR3��1

wait�� clrc xf ���ر�xf��ֹͣ����

mar ����ar2 ����AR3��Ϊ��ǰ�Ĵ���

in ����0fff6h ������IOSR�Ĵ�����״̬

bit ����4 ������12λ�Ƿ�Ϊ0

bcnd cont��tc �����Ϊ0���ȴ�ֱ��IOSR

�ĵ�12λΪ1

b wait

skip�� splk #0020h��ifr �����ж�

clrc intm

mar ����ar4 �����������1

banz uart1��ar3 ��δ���꣬������UART1�� ����һ����

ret ������

inpt1�� ret

inpt23�� ret

timer�� ret

uart�� ret

codtx�� ret

codrx�� ret

��end

TMS320F206 DSP ͼ��ɼ��� ������£�

- TMS320F206��Χ��·������� (04-17)

- ����TMS320F206 DSP��ͼ��ɼ������(06-26)

- DSP���ĵ�ģ���е�Ӧ��(08-20)

- ����DSP TMS320F206�ķ������ (07-06)

- ����TMS320F206�Ķ�Э�����ݴ��� (09-25)

- ����DSP����I2C��������������Ƽ�Ӧ��ʵ��(03-11)