基于DSP的近距离无线通信的嵌入式数据记录系统设计

引言

"黑匣子"是比较流行的电子记录设备之一,广泛应用于实时记录飞机、船舶、汽车等行进过程中的重要数据,包括速度、方向、高度、偏转角、发动机的转速和温度等。通过这些数据可以了解其运行过程中的情况,同时也是故障检测、分析事故原因的重要依据。在工业领域,常见的记录仪有压力记录仪、温度记录仪、湿度记录仪等,用于对生产环境进行实时监测,从而保证了有效生产和安全生产。

记录仪的数据下载方式通常有两种:通过传输线缆下载和通过插拔存储卡下载。前者需要连接线缆,后者需要插拔存储卡,两者均需要结构方面的拆卸。但在某些应用环境中,记录仪不便于拆卸,特别是在一些辐射性强的工业现场,更不适于长时间的近距离接触。另外,这两种方式在一定程度上均可能降低系统的可靠性。

本文依据某工业现场电子设备数据记录的需求,提出了一种基于近距离无线通信的数据记录设备。该设备以红外或蓝牙方式下载数据,与传统的数据下载方式相比,下载数据时既不需要拆卸设备连接线缆或插拔存储卡,又减少了连线和插拔存储卡可能导致的接触故障。

1 设计需求

在某工业现场电子设备工作过程中,要求记录系统能够实时记录设备的各种电气信号及其工作时序,用于事后设备运行状况的分析以及故障排查、定位。需要实时采集记录的信号包括2路ARINC429信号、10路TTL数字信号以及16路模拟信号。采样频率应大于或等于1 kHz,记录时间为1 h左右。根据信号通道数量、数据采集速率和数据记录时间,可估算出记录系统的存储容量应大于500 MB。通常,微处理器内部的存储空间有限,故需要将采集到的数据存储到存储容量大、具有非易失性的外部存储器中。本系统使用Sandisk公司的1 GB工业级CF卡作为存储设备。

2 系统总体设计方案

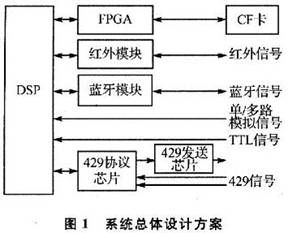

系统采用DSP和FPGA协同控制的方案,总体设计方案如图1所示。DSP主要完成数据的实时采集和控制,FPGA的数据传输,以及与无线通信模块的数据传输;FPGA则实现数据缓存和读写CF卡的逻辑时序控制。

DSP是主控制器。选用TI公司的16位定点DSP芯片TMS320F240。它的指令周期为50 ns,内部具有544字的RAM、224K字的可寻址存储空间、双10位模/数转换器、28个独立可编程的多路复用I/O引脚、1个异步串行通信口(SCI),以及1个同步串行通信口(SPI)。其内部资源可以满足系统对TTL信号和模拟信号的采集需求,通过外接ARINC429、红外和蓝牙专用接口芯片,实现ARINC429数据信号的采集和两种无线方式的通信。

FPGA是辅助控制器,其核心为FIFO和逻辑控制电路,用于完成DSP和CF卡间数据传输。选用Altera公司CyclonelI系列的FPGA芯片EP2C20-Q240C8。它具有142个用户可使用I/O引脚、52个M4K嵌入式阵列块和18752个逻辑单元。DSP和FPGA丰富的内部资源很好地满足了系统设计的需要。

系统主要包括数据存储和数据下载两大功能:

①数据存储。DSP实现对2路ARINC429信号、16路模拟信号和10路数字信号的实时采集,并将数据实时存入FPGA的FIFO中。当FIFO存储了一定量数据时,FPGA控制逻辑电路自动将FIFO中的数据写入CF卡中。

②数据下载。首先,DSP将系统的蓝牙和红外模块设置为从设备。当接收到工作人员所持的带有蓝牙或红外接口的地面设备发出的连接请求后,先进行鉴权,鉴权通过后与其建立连接。然后,FPGA控制逻辑电路读出CF卡中数据并存人FIFO,DSP通过查询或中断方式将FIFO中的数据通过无线通信模块发送给地面设备。

3 各功能模块设计

3.1 FPGA功能模块设计

使用FPGA实现异步FIFO模块和CF卡读写模块,是本设计的重点,也是难点。

3.1.1异步FIFO模块

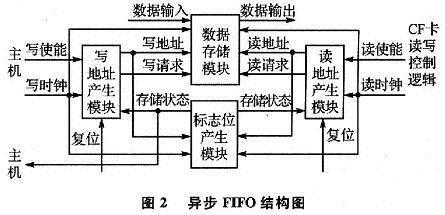

数据记录设备的实时性强、数据量大。为了提高数据传输速度、避免数据堵塞,利用FPGA硬件设计上的灵活性,在其内部构建了一个宽度为16位、深度为512的异步FIFO模块,作为DSP与CF卡之间数据传输的中继站。

异步FIFO的结构图如图2所示。它包括4个模块:数据存储模块、写地址产生模块、读地址产生模块和标志位产生模块。FIFO的读写采用读时钟和写时钟两个时钟。写时钟同步的信号有写地址产生模块生成的写请求和写地址;读时钟同步的信号有读地址产生模块生成的读请求和读地址。写使能和读使能分别由DSP与FPGA数据传输控制逻辑和CF卡读写控制逻辑生成。标志位产生模块由读写地址关系生成FIFO存储状态标志,并反馈给主机DSP。DSP通过查询该标志来控制与FPGA的数据传输。

3.1.2 CF卡读写模块

CF卡读写模块分为CF卡读控制模块和CF卡写控制模块。CF卡读或写模块的设计具有相似性。这里仅介绍写CF卡的工作过程。

首先,设置CF卡的属性寄存器。CF卡有4个属性

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)