基于DSP/FPGA的以太网控制器的运动控制器设计

脉冲输出电路由FPGA内部精插补器完成,精插补器根据DSP发送来的粗插补数据产生均匀的脉冲输出,脉冲的输出有两种格式:"脉冲+方向"和"正负脉冲"。由于差分信号对外部电磁等信号有很好的抗干扰性,特别是对共模干扰有很好的抑制作用。所以脉冲经过光耦隔离后,再将信号接入差分线驱动器AM26LS31后输出,差分线驱动器AM26LS31的作用是将输入的单极性方波信号转化为一对极性相反的电机驱动信号。

3.4编码反馈电路设计

电机编码信号直接传入电机驱动器中,电机驱动器将三对差分编码信号A+,A-,B+,B-,N+,N-作为反馈传给运动控制器。在电机旋转时,所发出的编码信号会出现非常多的毛刺,并且经过驱动器大电源的干扰,如果直接接到FPGA中,可能会引起误判断,所以先将三对编码信号经过差分芯片AM26LS32转化成单路信号A,B,N后再接入FPGA中。芯片AM26LS32功能是将输入的一对极性相反的编码器差分信号转化成单极性的脉冲信号,与AM32LS31正好相反。

3.5开关量接口和通用I/O电路设计

输出信号包括复位信号和使能信号,由FPGA产生,经光耦隔离后直接输出;输入信号包括驱动报警信号,正负限位信号和原点信号,这些信号经光耦隔离、电平转换后再由FPGA接收,当FPGA检测到这些信号后,确定具体的触发信号,做出相应的反应。另外运动控制器还提供了八路数字量输入通道和八路数字量输出通道,输入、输出通道都经光电隔离,以提高抗干扰性。

4网口模块设计

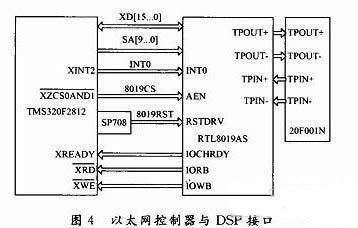

DSP通过以太网控制器RTL8019AS与上位机连接,RTL8019AS在一块芯片上集成了RTL8019AS内核和一个16KB的SDRAM存储器,兼容RTL8019AS控制软件和NE20008b或16b传输,其接口符合Ethernet2和IEEE802.3标准。RTL8019AS与主机的接口模式有三种模式:跳线模式,PnP模式,RT模式。此运动控制器使用便于DSP应用的跳线模式。DSP与RTL8019AS的连接如图4所示。

(1)数据总线和地址总线。RTL8019AS的数据总线和DSP的16位数据总线直接相连即可。RTL8019AS片内NE2000寄存器组都是通过其映射I/O端口进行访问,I/O端口共32个,地址偏移量为00H~1FH,把I/O基地址设为300H,则对应的I/O端口寻址范围为:300H~31FH。只需要10根地址线就可以对I/O端口进行寻址,把SA10~SA19接低电平,SA0~SA9按照表1接法即可。

由表1可以看出,只需要5根地址线就可以寻址32位I/O端口,所以可以直接把SA9,SA8接高电平,SA5~SA7接低电平,SA0~SA4与DSP的低5位地址线XA0~XA4相接。

(2)控制总线。RTL8019AS片选信号AEN使用DSP的扩展片选信号,IORB、IOWB直接与DSP的读写控制信号

相连,中断输出引脚INT0与DSP的XINT2相连,高电平有效的复位输入引脚与监控电路芯片SP708的RST相连,当DSP复位时,RTL8019AS也复位。

(3)RTL8019AS与网络介质接口。RTL8019AS可以使用同轴电缆或双绞线作为传输媒介,将其AUI接口接地或悬空,使用BNC接口。BNC接口方式支持8线双绞线或同轴电缆。20F001N是双绞线驱动器,为耦合隔离变压器模块,通过它可以去除因电路数字特性导致的高次谐波。RTL8019AS与20F001N的连接如图4所示。其差分输入信号TPIN+、TPIN-与差分输出信号TPOUT+、TPOUT-分别与20F001的对应引脚相连。

5结语

在PC平台下,充分利用了DSP的数据处理能力和FPGA的硬件特性,使系统既能进行复杂的轨迹规划、高速插补,又能保证运动控制器的稳定性和精确性,这种运动控制器能应用于数控系统,机器人制造等控制领域。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)