基于DSP/FPGA的以太网控制器的运动控制器设计

0引言

运动控制技术是制造自动化的关键基础,其水平高低是衡量一个国家工业现代化的重要标志,研究和开发具有开放式结构的运动控制器是当前运动控制领域的一个重要发展方向。随着集成电路技术、微电子技术、计算机技术和网络技术的不断发展,运动控制器已从以单片机和微处理器作为核心的运动控制器和以专用芯片(ASIC)作为核心处理器的运动控制器,发展到了基于PC机平台的以数字信号处理器(DSP)和现场可编程门阵列(FPGA)作为核心处理器的协处理架构的开放式运动控制器。该控制器将PC机和DSP的信息处理能力与FPGA的外围扩展功能很好的结合在一起,具有信息处理能力强、模块化、开放程度高、运动轨迹控制精确等优点。

1系统概述

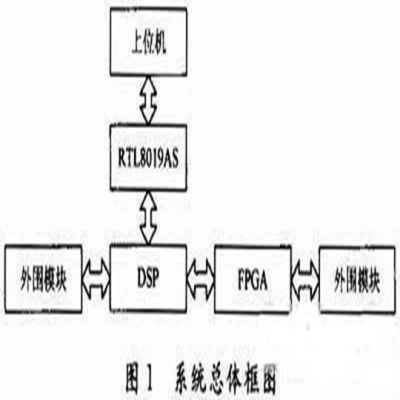

该四轴运动控制器系统以TI公司C2000系列DSP芯片TMS320F2812和alterA公司CycloneⅡ系列FPGA芯片EP2C8F256C6为核心,DSP通过网口接收上位机的控制参数,完成系统位置、速度控制及运动轨迹规划;FPGA完成运动控制器的精确插补功能和外围电路的扩展,系统总体框图如图1所示。

运动控制器的主要功能包括:4路模拟电压输出,电压范围为-10~+10V,分辨率为16b;4路脉冲量信号输出;4路脉冲方向信号输出;4路驱动复位信号输出;4路驱动使能信号输出;4路差分编码信号输入;4路驱动报警信号输入;8路正负限位信号输入;4路原点信号输入;16路通用数字量。I/O。

2DSP模块设计

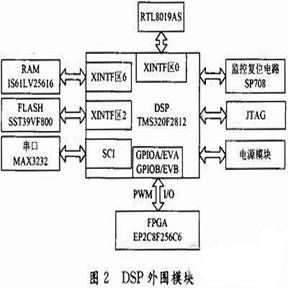

DSP根据从上位机接收的运动模式和运动参数实时计算规划位置和规划速度,生成所需的速度曲线,实时的输出规划位置。TMS320F2812是TI推出的一款专门用于电机控制的32位定点DSP芯片,采用高性能静态CMOS技术,主频高达150MHz(指令周期6.67ns),低功耗,核心电压为1.8V,I/O电压3.3V,支持JTAG边界扫描,128K×16b的片内FLASH。有两个事件管理器(EVA和EVB),它们都是特定的外围设备,为多轴运动控制器而设计的。可通过外部存储器接口XINTF扩展外部存储器。DSP外围模块设计如图2所示。

为增强抗干扰性,DSP通过以太网控制器RTL8019AS与上位机连接,RTL8019AS内部含有一个16KB的SDRAM,DSP通过外部存储器接口对其进行读写来接收上位机的命令或向上位机传送反馈信号。在数据处理过程中要占用大量的存储空间,DSP内部仅含有18K×16b的SARAM和128K×16b的FLASH,存储空间显得过小,所以通过外部接口扩展了256K×16bRAM和512K×16bFLASH,RAM和FLASH芯片分别选择IS61LV25616AL、SST39VF800,它们都具有接口简单、读写速度快等优点。SCI模块用于扩展RS232串行通信接口,串口芯片使用MAX3232。

运动控制器所需电压为5V,3.3V,1.8V,1.2V。输入电压5V,分别采用稳压芯片LM1085IS3.3,LM1117-1.8将其转换成3.3V和1.8V,由于TMS320F2812的I/O电压3.3V要先于内核电源上电,所以1.8V要由3.3V降压得到,以确保上电次序。1.2V是FPGA内核所需电压,由稳压芯片LM317S稳压得到,LM317S的输出电压范围为1.2~25V,复位电路采用SP708低功耗微处理器监控器件,此器件有众多的组件,有效的增强了系统的可靠性及工作效率。

3FPGA模块设计

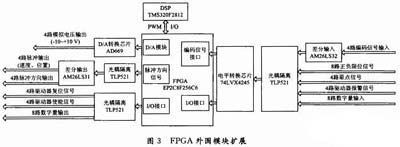

FPGA用于轴资源的扩展,当接收到DSP中的规划位置后,在轴资源中对其进行变换处理,输出到伺服控制器中,伺服控制器将规划位置与编码反馈的计数位置进行比较,获得跟随误差,并通过伺服控制算法得到实时的控制量,将控制量传递给D/A转换器,由D/A转换器转换成控制电压输出。

EP2C8F256C6是alterA公司CycloneⅡ系列芯片,其特点为高性能低功耗,内核供电电压为1.2V,8256个逻辑单元(LEs),182个用户I/O口(项目中使用了157个I/O口),165888b的内部RAM,嵌入了18b的乘法器,每个乘法器又可拆成2个9b的乘法器,芯片内部含有2个锁相环(PLL),8个全局时钟(GlobalClocks)。该芯片所具有的逻辑单元数、频率和用户I/O口等都能很好的满足设计需求。FPGA的外围模块扩展如图3所示。

3.1与DSP接口设计

DSP芯片的事件管理器(EVA,EVB)用于和FPGA连接,当输出脉冲量控制驱动器时,DSP使用两个事件管理器进行PWM波的控制,当输出模拟量时,DSP使用GPIOA/GPIOB向FPGA输出规划位置。

3.2模拟信号输出电路设计

采用D/A转换器AD669进行模拟信号的输出,AD669具有两级锁存,在设计中,将其四路D/A芯片的第一级锁存处于透明状态,第二级锁存控制信号LDAC连在一起,当四路D/A芯片的数据预装好后,打开第二级锁存,四路D/A芯片即可同时转换,实现了四轴驱动的同时控制。

3.3脉冲信号输出电路设计

脉冲输出电路由FPGA内部精插补器完成,精插补器根据DSP发送来的粗插补数据产生均匀的脉冲输出,脉冲的输出有两种格式:"脉

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)