基于DSP的变电站综合自动化系统设计

引言

变电站综合自动化系统是将变电站的二次设备经过功能组合和优化设计,综合利用先进的多种学科技术,集成于一体的自动化系统[2][4]。从系统的结构看,全分散式的设计思想越来越显现出优越性。由于变电站的数据量和信息量大,实时性要求高,则将高性能DSP应用于变电站综合自动化的设计方案中。其内部哈佛结构使数据空间和程序空间分离,独立的总线和程序总线允许程序数据同时操作;具有独特的逆寻址方式,能高效的进行快速傅立叶变换运算降低了软件的编写困难;采用内存映射方式管理I/O,能灵活方便的扩充外围电路。

1 系统的整体结构设计

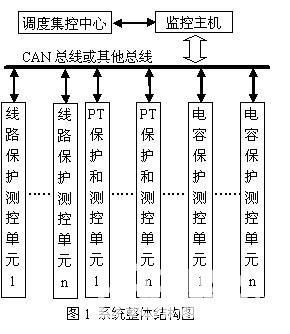

采用TI 2000系列的TMS320F2812芯片为核心处理器,整体采用全分散式结构,集监测、保护、控制、远动等为一体的综合系统。系统整体结构如图1所示:

主要保护和测控单元有:(1)线路保护和测控单元;(2)主变差动和测控单元;(3)主变后备保护和测控单元;(4)电容保护和测控单元;(5)备用电源自投和测控单元;(6)电动机保护和测控单元;(7)PT保护和测控单元;(8)中央信号单元;各个保护和测控单元分散安装在监控室或一次设备附近,便于安

装,维护管理。监控主机发命令给各个单元和远方调度集控中心,进行实时数据传输和信息交换。

2 各单元硬件电路设计

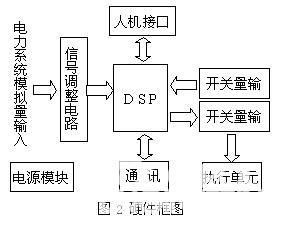

本系统各个保护和测控单元的硬件结构相似,分模拟量输入,核心处理器,开关量输入、输出,人机接口,通讯和电源模块六大部分。系统的硬件结构如图2所示:

2.1模拟量输入

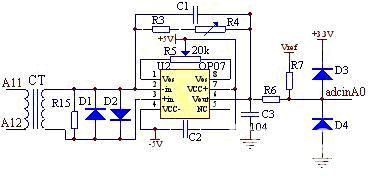

模拟量有线路电压、电流,及其频率,变压器油温、变电站室温等等。电力系统的电压电流信号不能直接送到A/D器件的输入端转换,而要先经PT,C T(密互感器CT05)将电压电流降低,再经精密互感器(TV)和信号调理电路(OP07,C1,R3,R4,R5),电位提升(R6,R7),限幅作用(D3,D4),限制进入DSP的电压范围在0~3V。线路电流采集电路如图3所示:

图3 模数转换前置电路

2.2 核心处理器[3]和电源模块

CPU选用TI公司TMS320F2812 DSP芯片,最高频率可达150MHz。通过软件?

编程可对实时采集的数字信号在短时间内进行快速傅立叶变换,即可直接提取出所需要的各次谐波进行计算和继电保护,软件和硬件的设计难度大大降低;在结构上,内部集成了丰富的外设,自带两组8选1 的12位A/D输入端口,可实现并发和级联采样两种模式,已很好的满足实用需要,可实现真正的同步采样,提高了采样点的实时同步性;可支持eCAN(enhance Controller Area Network),RS232,RS485,LONWORKS,以太网,光缆,无线等等多种形式的通信。指令系统采用流水线操作,减小了指令周期到6.67ns,大大提高了计算速度和实时性;采用内存映射方式管理I/O,能灵活方便的扩充外围电路。在性能上,具有八级流水线,完全可以避免从同一地址进行读写而造成的秩序混乱。

电源采用TPS767D318电源转换芯片实现DSP所需的1.8V,1.8VA,3.3V,3.3VA电压,其中模拟地和数字地用小电阻或磁珠连接,防止电磁干扰。

2.3开关量和人机对话部分

开关量输入、输出部分是微机保护与外部设备的联系部件,采用光电隔离器件,起信号隔离和电平转换的双重作用,主要用来接受来自外部设备的开关量输入号和向外部设备发送开关量信号。

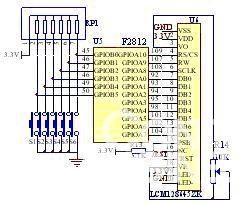

人机对话部分包括按键(6个)、3.3V供电的液晶LCM128645ZK显示器,打印机及信号灯、音响及语音报警等,利用DSP的GPIOA,B口,连接按键和液晶,如图5所示:

图4 键盘与液晶显示电路

2.4通讯

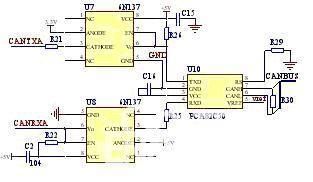

该模块实现各子系统之间,及其与监控主机之间的信息传输。TMS320F2812自带1个eCAN和2个SCI和1个SPI通讯接口,可同时支持eCAN,RS-232和RS-485总线多种通讯形式。eCAN总线连接方便,而且具有优良的错误处理机制及可靠的数据传输性能,很好的满足变电站综合自动化的要求。

图5 DSP与eCAN总线接线图

3 软件主要实现的功能

3.1 测量功能

采集各个被测线路的电压、电流以及频率,及变压器油温和变电站室温等模拟量信号,断路器、隔离开关状态、变电站一次设备及报警信号、变压器分接头位置等数字量信号等[3]。下面是AD电压采集的部分程序,采用并发采样双序列发生器模式,对二次回路中A、B、C三相和零序的电压电流进行采集。

AdcRegs.ADCTRL3.bit.SMODE_SEL=1;//设置并发采样模式

AdcRegs.ADCMAXCONV.all=0x0011;//2个双重序列发生器

(总共4个)的CONV

AdcRegs.ADCCHSELSEQ1.bit.CONV00=0X00;

AdcRegs.ADCCHSELSEQ1.bit.CONV01=0X01;

AdcRegs.ADCCHSELSEQ3.bit.CONV08=0X02;

AdcRegs.ADCCHSELSEQ3.bit.CONV09=0X03;

……

interrupt void adc_isr(void)

{

Voltage11[ConversionCount]=AdcRegs.ADCRESULT0;//Ua

Voltage12[ConversionCount]=AdcRegs.ADCRESULT1;//Ia

……

Voltage41[ConversionCount]=AdcRegs.ADCRESULT7;//U0

Voltage42[ConversionCount]=AdcRegs.ADCRESULT7;//I0

if(ConversionCount=1023)

{

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)