基于DSP的汇编程序优化

可以将原来不能并行的从内存中取数语句和对寄存器赋值语句(这两条语句都要到总线资源)并行起来。这在许多参考资料中都可以见到。在此不再列举具体实例。

(4)增加取数个数达到并行

某些DSP还支持联合取数的功能,其寄存器可能是32位.但是却支持64位数据的存取,即一条语句可完成二组数据的存取。而对这两组数据的处理却是相互独立、可以并行的,利用这一功能来达到优化,也不失为一种好方法。

2.2 利用软件流水

流水技术是提高DSP程序执行效率的另一种主要手段。它可以使若干条指令的不同执行阶段并行处理。有时由于相邻的几个指令行有可能使用相同的资源,其间又可能有相关性,从而使DSP在执行时自动插人延迟,使DSP的运行速度比预期的慢:有时又可能由于指令本身的原因造成延时(例如跳转指令),使得DSP的效率降低。由于流水技术本身的复杂性以及DSP硬件结构的多样性,这里不再讨论造成这种延迟的种种原因(事实上各个DSIC的使用手册中均有详细的说明),只是想告诉读者其实有时候只需要移动几条指令的位置就可以达到优化的目的。在这里仍继续采用实例1的代码段作为例子(TI公司C6000系列电路的编程更适合此例,只是其汇编指令太复杂)。

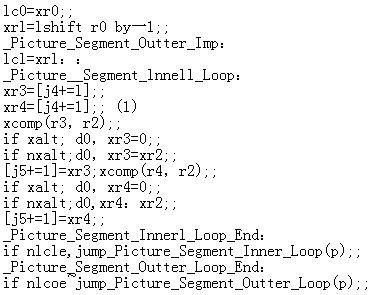

如实例5(1)所示,它将例3中并行的语句重新分开,变为二条语句执行。计算其效率可以发现平均每个像素仍然花费5.12个指令周期,与将其并行的效率相同。这是因为取数与比较这二条指令共用了同一寄存器资源xr3,造成这二条语句间插入一个指令周期的延迟,而把语句插入到这两条指令之间,恰恰利用了这一延迟,达到了优化的效果。

实例5:

对汇编程序进行优化,应综合上面提到的各种方法。首先使循环内各语句在时间关系上尽量相互独立.然后利用种种技巧最大限度地使语句并行;最后再考虑软件流水造成的延时,调整各条语句的位置.尽量减少延时。

3 结束语

对特定DSP汇编程序进行优化的过程就是对其芯片结构充分熟悉利用的过程,程序优化与精简的程度正比于对芯片结构的熟悉程度。这是一个不断深入、永无止境的过程。但是还应看到,在程序达到高效的同时,牺牲的是程序应有的可读性。在软件高度产业化的今天,程序的可读性有时甚至比其高效性更为重要。因此如何在程序达到高效的同时尽量保证其可读性也是在对程序进行优化时应着重考虑的问题。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)