基于DSP的汇编程序优化

1 引言

数字信号处理器(DSP)相对于模拟信号处理器有很大的优越性,表现在精度高,灵活性大,可靠性好,易于大规模集成等方面。随着半导体制造工艺的发展和计算机体系结构的改进,数字信号处理器的功能越来越强大,对信号处理系统的研究重点又重新回到软件算法上,而不再像过去那样过多地考虑硬件的可实现性。随着DSP运算能力的不断提高,能够实时处理的信号带宽也大大增加,数字信号处理的研究重点也由最初的非实时性应用转向高速实时应用。

目前大多数DSP虽然都支持C语言编程,但是在实际工程应用中,最常用的方法是用C语言编写流程控制。搭建工程框架,具体的算法模块及比较耗时的功能模块还是采用汇编语言来编写。这是因为C语言虽然具有易读性、可移植性等优点,但是它不便于对系统硬件资源的直接控制,无法发挥DSP自身的特点,无法充分利用DSP系统结构中有限的资源。特别是在硬实时性系统中,用汇编语言进行编程可利用DSP自身硬件结构的特点对汇编程序进行优化与精简,往往能够使一些复杂的算法和功能模块在实时性方面取得非常好的效果。

2 汇编程序优化

DSP的种类繁多.各类DSP都有其自身的硬件特点,而对DSP汇编程序进行优化的过程就是根据程序自身特点充分利用DSP硬件资源的过程。因此,具体到不同的器件.其优化方式也不尽相同。目前比较流行的大多数DSF,都支持程序并行和软件流水,本文从这二方面出发,概括归纳出对汇编程序进行优化的一般方法。希望能够在对不同DSP汇编程序优化的过程中提供一些思考方式上的切人点。为了易于说明,笔者提供了一些实例,这些例子均是用AD公司TSl01系列电路的汇编语言编写的。

2.1 加强程序并行

程序的并行是汇编优化的关键。但是,在开始进行任何优化之前,必须了解从何处着手,首先了解瓶颈在何处。软件的某些部分可能只执行一次(初始化)或者只执行少数几次,费尽心思优化此部分代码并非明智之举,因为获得的整体节省效果是微乎其微。对程序的优化应将主要力量集中在最为费时的部分。

(1) 循环展开达到并行

通过对大量DSP程序的研究.可以发现整个程序比较耗时的部分往往是在1个或几个大的循环中。这些循环部分又往往可分为取数、处理、储存处理结果3个顺序执行的步骤,这3个步骤有明显的时间先后关系.只有取了数才能处理。处理后才能存储结果,这种时间上的相互依赖性为程序的并行带来了非常大的困难。

循环展开是最常用的一种优化技巧。1次循环处理过程中的各语句是具有很强的时间先后顺序的,但是在连续2次循环过程中的各种语句却是相互独立的,它们是以相同的语句处理不同的数据。因此可以采用将循环次数减半,每2次(也可以是3次、4次等,应根据具体情况来确定,同时循环次数要做相应改变)循环合并为1次循环过程的方法来使程序并行,提高效率。

例1是一段对图像进行二值化的代码的主要部分.是一段2次的循环,并未经过优化;实例2是将其循环展开,2次循环过程合并为1次循环的代码段(这里假设其每行像素个数为偶数,如果不为偶数只需在内循环外额外处理一个像素即可);实例3是循环展开并进行优化精简后的代码段。这3段代码均用TSl01的汇编语言编写,其中j4指向待处理的图像;i5指向处理后的图像;xrO、xrl分别为图像行、列个数;xr2为二值化的阈值,像素灰度值大于或等于该值的使其等于该值,而像素灰度值小于该值的设为零。

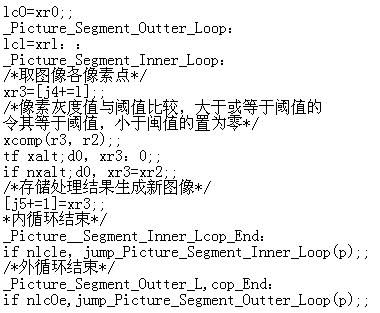

实例1:

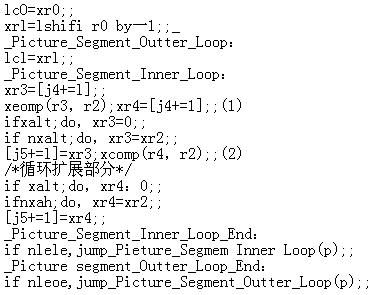

实例2:

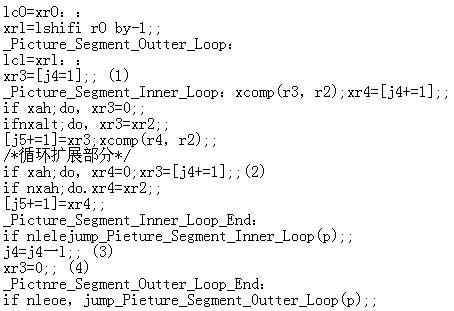

实例3:

如实例3中的(1)、(2)所示,下一循环的取数和与阈值比较语句同上一循环中的指令达到了并行。分别运行实例1与实例3并计算其每个像素所花费的时间,可知实例1中平均每个像素花费7.12个时钟周期,而实例3中平均每个像素花费5.12个时钟周期,比优化前少用了差不多2个时钟周期。

(2)提前取数达到并行

在循环外提前取数,彻底打破循环中各指令间时间的先后顺序,增强其独立性并最终达到并行的目的,这也是一种常用的方法。实例4利用此种方法,在实例3的基础上对实例1的代码段做了进一步的优化与精简。

如实例4中所示,(1)在循环外提前进行了取数,并在(2)达到了并行,(3)、(4)对由于提前取数造成的指针移位和额外的赋值进行了修正。但是,在使用此方法进行精简优化时要特别注意循环结束后对指针的修正。经计算。实例4平均每个像素所花费的时间为4.18个指令周期。

实例4:

(3)改换语句达到并行

有时,不同的语句利用不同的硬件资源可以得到相同的结果。换一条语句执行.改变原语句所用硬件资源。往往也能够增加程序的并行程度。例如DSP中往往提供独立的加法、乘法运算单元,同样一条赋值语句可以用加0或者乘l代替,这样就

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)