基于DSP的称重控制器设计

1 引言

在玻璃行业中, 通过电振机或绞龙电机供料是技术成熟并被广泛采用的方法, 其优点是结构简单控制方便。在此基础上设计的称重控制器大多以传统单片机为核心。相对传统单片机, 数字信号处理器在实时性,高速运算等方面的优势巨大,将逐步成为工业控制的主流选择。本设计针对玻璃配料过程中存在的称重精度不高, 自动化程度不高等问题, 采用了高性能数字信号处理器TMS320F2812(F2812)作为核心器件。控制器在设计了友好人机界面的基础上,专门设计了与F2812内置模数转换器相匹配的放大电路,并在A/D 采样过程中加入了采样校准的方法,保证采样数据更加准确;采取数字滤波方法处理采样数据,滤除采样数据中的干扰。

2 配料系统工作流程

玻璃配料系统一般包括称重控制器、备料斗、计量斗和相关动力装置。备料斗用来存储一定量的待测物料, 备料斗下方的出料口由电振机的驱动, 通过改变电振机的振动速度可以改变备料斗的出料的速度。备料斗下方是计量斗,它是一个放置在称重传感器上的悬浮容器,控制器通过解读传感器的数据得到计量斗内的物料质量。

当开始称重过程时, 称重控制器发出控制信号, 备料斗开始快速下料, 物料进入计量斗后, 由计量斗下方的传感器测得重量信号, 信号经处理还原为物料的重量。控制器自动比较当前的物料重量与目标重量的偏差,当偏差值E 缩小到一定范围时(如10%,即达到目标重量的90%),发出信号并驱动备料斗进行慢速下料,使测得的重量值变化减缓,有利于精确控制。每当控制器发出停止加料信号时,会有一定量的物料刚刚脱离电振机出口正在下落(即"飞料"),使最终称得的物料重量要大于系统判定的目标重量。一般采取的解决办法是在达到目标值之前提前停止加料, 等待"飞料"落下, 待检测值稳定后,控制器再进行偏差值的判断并进行下一步的控制(即点动加料模式), 直至重量达到目标值。然后控制器发出信号, 打开计量斗排出称重完毕的物料,完成一次称重控制过程。结合以上工作过程控制器设计如下。

3 控制器硬件实现

控制器硬件框图由图1 给出, 主要由F2812、信号调理电路、显示/ 键盘模块、串口通信模块组成。F2812作为一款32 位的数字信号处理器, 采用哈佛总线结构,计算能力强,最高运行速度达到150MIPS,能够处理包括称重控制和软件滤波等多种算法;内部包括128KB 的闪存(FLASH)和128KB 的只读存贮器(ROM),存储空间大可满足大部分程序设计要求;支持45 个外围中断, 响应迅速,方便子程序的快速调用;片上集成了12 位A/D转换器,能够快速地进行模数转换,在系统设计时不必增加额外的硬件;具有两个串行通信接口(SCI)以及一个串行外围接口(SPI),可简化通讯接口设计,使系统紧凑。

图1 系统硬件框图

3.1 信号调理电路

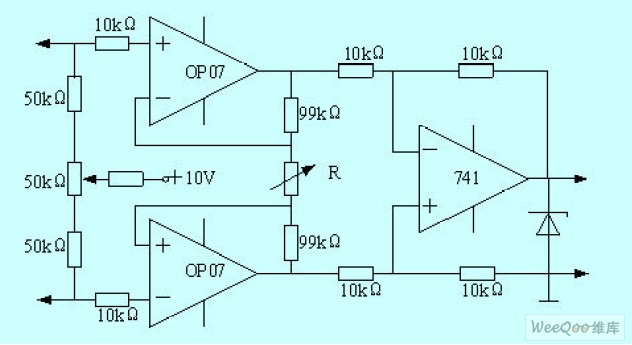

图2 放大电路原理图

信号调理电路主要完成模数转换前的信号的滤波和放大, 由于本设计采取软件滤波, 所以主要考虑信号的放大问题。在现场应用中,以10V 电压激励灵敏度为2mV/V 的称重传感器,其满量程输出信号电压为20mV。F2812 内置A/D 转换器的输入电压为0-3V,所以必须设置放大电路。设计采用由3 个运算放大器组成的仪用放大电路(图2)。电路中左侧两个OP07 组成第一级差分放大电路,右侧OP07 为第二级差分放大, 调节1k Ω可变电阻即可调节电路的增益。经计算要使增益调节达到15 0 倍,需要将可变电阻R 调节到1.33 Ω。采用此种电路输入阻抗高,共模抑制比高。为了防止意外情况下输入电压超过DSP 的工作电压而损坏芯片,在信号输入DSP 引脚之前还需外接一个3V 的稳压管。

3.2 A/D 转换与采样校准

A/D 转换的精度将很大程度上决定称重控制器的精度。本设计采用F2812 自带的模数转换器,这样可以在达到控制器所要求转换精度的基础上简化电路设计。

增益误差和偏移误差是影响A/D 转换精度的主要因素。增益误差是指实际传输函数的斜率与理想传输函数的斜率的差别;偏移误差是指输入为零时实际输出与零的偏差。本设计采用了采样校准的方法补偿增益误差和偏移误差。F2812 的一组A/D 转换单元内8 个通道之间的误差典型值小于0.2%,通过采样另外2 个采样通道的已知参考电压H x 、L x , 得出A / D 转换结果H y 、L y ,再利用求解线形方程组的原理计算出增益误差和偏移误差,然后计算出较精确的转换结果。y 为待校正量, 则校正后的结果x 可由式1 表示:

F2812 芯片本身设计有A/D 转换采样校准的参考电压,分别由ADCREFP、ADCREFM 引脚输出,电压分别为2V、1V。使用时外接10 μ F 的低等效串连电阻陶瓷旁

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)