基于Matlab/DSP Builder任意波形信号发生器的两种设计

双击图2或图4中SignalCompiler,在弹出的对话框中点击"Compile",DSP Builder将会调用QuartusⅡ进行全程编译,这个过程包括创建QuartusⅡ工程、综合和适配。会自动将mdl文件转换为QuartusⅡ能够识别的VHDL源程序。

打开QuartusⅡ9.O环境,打开DSP Builder自己建立好的工程,最后选择cycloneⅡ系列的FPGA芯片EP2C8Q208C,锁定好相关引脚,再将.sof文件下载到EP2C8Q208C芯片中。

完成下载后,传统的方法是用逻辑分析仪接到FPGA的管脚上进行硬件测试,该方法繁琐且复杂,为解决此问题,可使用QuartusⅡ自带的嵌入式逻辑分析仪SignalTapⅡ进行硬件测试。

打开SignalTapⅡ,设置好所要观测信号的触发状态、采样时钟和数据深度,之后将文件保存为.stp文件,并添加到系统工程里,然后启动完整编译。

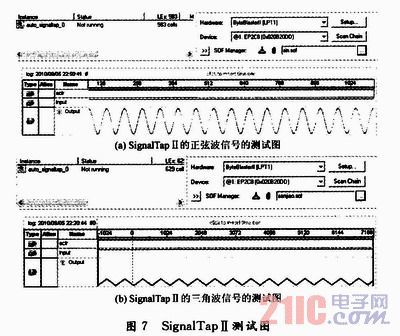

对传统方法下生成的正弦波信号和基于DDS生成的三角波信号进行SignalTapⅡ硬件测试,结果如图7所示。对比图7,图5和图6,表明两种设计方法的正确性。

将硬件电路接入高速D/A转换电路,用示波器检测D/A输出,会看到相应波形。

5 结语

基于Matlab/DSP Builder的系统实现方案形象直观,本文采用两种方法在DSP Builder下实现了任意信号发生器的设计,通过Simulink的系统仿真和SignalTapⅡ的硬件测试,证实了设计方法的正确性,取得了预期的效果。

DSP Builder作为Matlab/Simulink中的一个工具箱,使得用FPGA设计DSP系统完全可以通过Simulink的图形化界面进行,使用DSPBuil-der设计任意波形信号发生器的所有基本组件都已经存在,只需要对每个组件设置参数后逐一连接就可以,从而使得一个复杂电子系统设计变得相当容易而且直观,利用SignalCompiler很容易将模型转换为VHDL语言,不涉及到编程,操作更简单,开发速度大大加快。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)