基于Matlab/DSP Builder任意波形信号发生器的两种设计

0 引言

在当今的科技信息社会中,尤其是在电子设计和信号测试系统中,通常需要一些复杂、特定频率的信号,通常的信号发生器难以满足要求,市场上出售的一些任意信号发生器的价格昂贵,体积较大,不能满足实际的需要。

Altera DSP Builder是一款系统级的设计工具,依赖于Mathworks公司的数学分析工具Matlab/Simulink,可以在Sireulink中进行图形化设计和仿真,同时又可以通过signalCompiler把Matlab/Simulink的模型文件(.mdl)转换成相应的硬件描述语言VHDL,本文用两种方法,即传统型的任意信号发生器和基于直接数字频率合成(DDS)的任意信号发生器,在DSPBuilder的开发工具下实现任意信号发生器的设计,不涉及到编程,操作简单。

1 传统型任意信号发生器的设计

1.1 设计原理

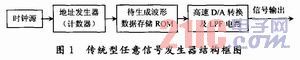

传统型任意信号发生器原理比较简单,将时钟源作为地址发生器(计数器)的输入时钟,通过改变时钟源的频率,可以实现调整地址发生器(计数器)产生地址的变化速率,从而达到改变输出波形与输出频率的目的。当地址发生器输出值等于待生成波形数据存储器中波形数据的地址时,待生成波形数据存储器将输出此数据到高速D/A转换,将其变为模拟信号,经低通滤波器后输出所需波形。D/A的输出频率fuot与待生成波形数据存储器的波形数据点数N以及时钟源的频率fclk关系为:

由式(1)可知,只要改变数据波形点数N就能控制输出信号的频率。

1.2 系统设计

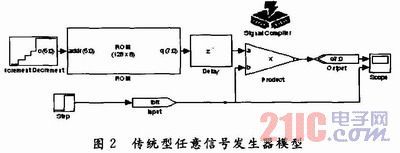

根据图1所示的原理框图,在Matlab/DSP Builder平台上,建立传统型任意信号发生器的Simulink模型,如图2所示。

在图2中,Increment Decrement模块起到一个地址发生器的作用,随着时钟的输入不断累加输出,ROM模块存放待生成信号的波形数据,输入模块input通过produt模块控制信号的输出。

利用Matlab强大的仿真功能,方便、快捷地生成给定频率、周期、脉宽的任意波形数据,但生成的数据通常是浮点型的,要将其转换为十六进制的Hexadecimal(Itel-Form)File(.hex)格式的文件,然后将*.hex文件添加到ROM存储器中,设置系统模型的参数,就可以得到任意信号波形。

2 基于DDS的任意信号发生器的设计

2.1 设计原理

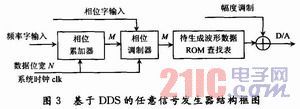

基于DDS的任意信号发生器结构框图如图3所示。由图3可以看出,相位累加器在系统时钟的控制下以频率控制字长的步长进行累加,输出的线性相位序列和相位控制字相加后对待生成波形数据ROM查表寻址,待生成波形数据ROM查找表输出相应波形的离散序列,再由DAC将其转换为模拟量,把存入的数据重新整合起来。此过程实际完成了相位到幅度的转换。

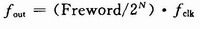

设系统时钟为fclk,频率输入字为Freword,相位输入字为Phaseword,N是相位累加器的数据位宽(频率输入字的数据位宽),相位调制器的位宽为M,则DDS的输出信号频率为:

输出信号的相移为:

由式(2)和式(3)可知,改变频率输入字和相位输入字就可以分别控制输出信号的频率和相位。

2.2 系统设计

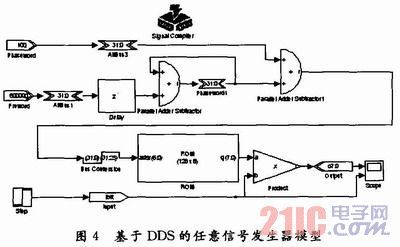

根据图3所示的框图,在Matlab/DSP Builder平台上,建立基于DDS的任意信号发生器的Simulink模型,如图4所示。

该系统中,共有三个输入:Freword为频率字输入、Phaseword为相位字输入、input为信号输入控制模块。ROM模块中装载要输出信号的波形数据。input模块通过product模块控制信号的输,Delay模块,Parallel Adder Subtractor模块和Phasewordl模块构成相位累加器,相位调制部分由Parallel Adder Subtractorl模块和Bus Conversion构成,加法器使用了Pipeline,内部已含寄存器,因而加法器出来后就无需再加延时模块。选择频率字为8 000 000,相位字输入为100。

同样,利用Matlab将待生成波形的.hex文件添加到ROM存储器中,设置各模块的参数,即可得到所需的信号波形。

3 系统仿真

只要将待生成信号的波形数据添加到图2或图4的ROM模块中,设置各模块的参数,就可得到任意所需波形,本文只给出传统方法下生成的正弦波信号和基于DDS生成的三角波信号的系统仿真。

3.1 传统型正弦波信号的系统仿真

由QuartusⅡ生成的正弦波信号的.hex文件如表1所示。

将正弦波的数据.hex文件添加到图2的ROM模块中,设置系统模型的参数,系统仿真结果如图5所示。

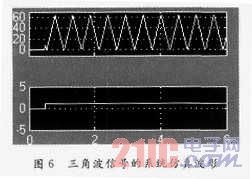

3.2 基于DDS的三角波信号的系统仿真

由QuartusⅡ生成的三角波信号的.hex文件如表2所示。

将三角波的数据.hex文件添加到图4的ROM模块中,设置系统模型的参数,系统仿真结果如图6所示。

4 系统的硬件实现与测试

双击图2或图4中SignalCompiler,在弹出的对话框中点击"Compile",DSP

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)