基于FPGA+DSP技术的Bayer格式图像预处理

元素补零)。过程如下:第1行图像读入第1个FIF0后,第2行图像开始读入左边第1个FD的时候,开始计算第1行RGB数据,这时候第2个FIFO没有数据,相当于在第1行的数据前面补零。第1 944行图像读入第1个FIFO后,第1 943行图像读入第2个FIFO的时候,开始计算最后1行(第1 944行),这时候第1个FD已经没有数据读入,相当于在第1 944行的数据后面补零。由于FD具有延时效应,所以在读写时,前1个FIFO开始读写时,再经过延时2个时钟周期,才到达后1个FIFO,所以相邻的FIFO读写使能信号要间隔2个时钟周期。

对列的操作也是如此,每一行的第1个元素读出到B、E、H位置时开始计算,这样每一列的第1个元素前相当于是零元素。每一行的最后一个元素读出到B,E,H位置时开始计算,这样每一列的最后一个元素后相当于是零元素。

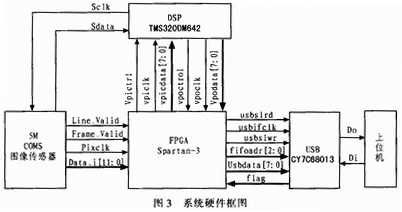

3 图像预处理系统的硬件工作过程

图像预处理系统硬件框图如图3所示,整个系统在通电后,先由TMS320DM642通过I2C向500万像素的CMOS摄像头发出控制命令,调整摄像头输出的图像分辨率、焦距等,之后由摄像头将采集到的图像数据发送至FPGA。由于摄像头输出的图像格式为12位的Bayer图像,而DSP的vp-ort口支持为8位或者16位的RAW采集方式,本项目中采用了更适合于DSP处理的8位数据,所以需要FPGA对采集的图像数据取高8位以方便DSP获取图像数据。FPGA在Frame_Valid和Line_Valid同时为高电平的时,在Pixclk的上升沿采样图像数据,并将原来的12位图像数据取其高8位转换成8位Bayer图像数据,然后利用FPGA内部的FD-FIFO模型结构取图像的3x3矩阵并利用双线性插值算法将Bayer图像转换成24位的RGB图像格式。除此之外,FPGA还将Bayer图像数据转换成了Y亮度信号以达到DSP对运算数据的要求,使得DSP只工作在核心算法上。

转换好的亮度图像数据由FPGA通过TMS320DM642的VPort1口发送至DSP进行核心算法处理。为了更好地达到整个DSP算法处理的实时性,DSP采用了BIOS实时操作系统。经算法处理好的图像数据由TMS320DM642通过其VPortO口发送至FPGA。图像预处理过程是在Spartan-3系列的XC3S1500x中进行的。FPGA使用的设计方法是HDL设计输入法,常用的HDL语言有VHDL和VerilogDHL语言,在本系统中使用VHDL语言进行硬件设计。

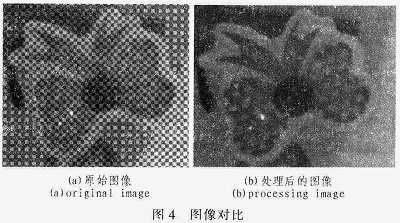

系统采用的是通过FPGA固件支持高传输率USB2.0的CY7C68013芯片,采用Slave_FIFO模式接收FPGA输出的图像数据,再通过USB口输送给上位机。如图4所示,图4(a)为RAW图像,即每个像素点只含有单一颜色分量的Bayer格式图像,图4(b)为系统处理后的RGB格式的亮度信号图像。

4 结论

可见,本文所提出的基于FPGA+DSP的图像处理系统,能在FPGA硬件设备中高速、高质量地对CMOS传感器采集的Bayer图像进行预处理,为DSP数字信号处理器进行核心算法减少运算量,提高整个图像处理的实时性,缩短了开发周期,并且这种FPGA+DSP的组合模式也可以推广到处理各种数字视频信号。

- FPGA构建高性能DSP(01-13)

- PCI-X总线图象处理技术(10-24)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)