基于FPGA+DSP技术的Bayer格式图像预处理

高分辨率图像实时处理在通信、医学、军事、航天航空、信息安全等领域有着广泛的应用和发展。在图像实时处理的过程中,下层图像预处理的数据量大,运算简单,但是要求运算速率高,可以用FPGA硬件来处理,上层所处理的数据量少,算法结构复杂,适于运算速度快,寻址灵活的DSP数字信号处理器进行处理。这里提出了一种FPGA+DSP相结合的实时图像处理系统,并应用于传像光线束传递图像。CMOS实际采集的是光线束的出端图像,FPGA将CMOS采集的Bayer格式的图像转换为RGB格式的亮度信号。由于光纤出、入端结构不同,需要DSP准确每根光纤的中心位置,重新排序才能输出正确的图像信息。该系统充分发挥了FPGA和DSP各自的优势,能更好地提高图像处理的实时性,降低成本。

1 Bayer图像格式

CMOS图像传感器作为一种基础器件可以实现信息的采集、转换以及视觉功能的扩展,并能直观真实地给出可视图像信息。系统中CMOS图像传感器输出2 592x1 944x12 bit的Bayer格式的图像(该格式的图像本身就是数字信号,因此无需对图像进行模数转换),Bayer图像格式如图1所示。在图l中,每个方格代表一个像素,并且只含有R、G、B中的一种颜色分量,奇数行由G、R像素交替构成,偶数行由B、G像素交替进行,其中G像素分量占所有像素的一半,R像素和G像素占另一半。因为G像素分量是R、B像素分量的2倍,所以如果G像素分量采用好的插值方法,不仅可以提高G像素分量的质量,也能提高R和B像素分量的质量。由于TMS320DM642的video port capture接口的数据总线是8位或者16位(该系统采用了更适合DSP处理的8位数据),所以为了后续的DSP能够更好的处理数据并减少DSP的运算量,需要使用FPGA先将输出的图像数据取高8位,然后依据每个像素点与相邻8个像素点之间的关系,使用双线性插值法将Bayer图像格式转换成24位的RGB图像格式和亮度信号,然后将处理后的数据发送给DSP。

2 图像数据处理的工作原理

2.1 Bayer图像的格式转换

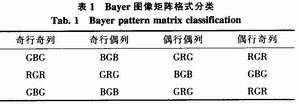

双线性插值法具有算法计算量少,算法结构简单,易于实现,占硬件资源少等优点,本系统中更适合FPGA实现。双线性插值法的基本原理是将每个像素位置上缺少的另外两种色彩分量通过该像素本身为中心的领域内具有相同分量的像素平均获得,即将每个像素的RGB分量都以该点像素为中心的3x3像素矩阵进行线性插值而成。按照这种思路可以将图像中的3x3矩阵分成4类,如表1所示。

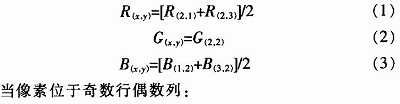

每种图像矩阵中间的像素点为待插值的数据源,设R(x,y)、G(x,y)、B(x,y)为插值计算后该点红、绿、蓝像素分量。当像素位于奇数行奇数列计算公式为:

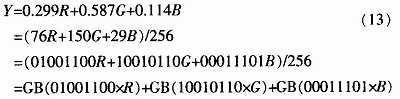

由于系统中TMS320DM642的视频端口使用的是8位RAW采集方式从CMOS传感器中采集图像,为了减轻DSP的运算负担,FPGA还需要将图像数据转换成Y亮度信号。将得到的RGB图像信号,通过浮点算法公式转换成亮度信号,具体推导公式如下(GB代表取高8位数据):

2.2 FPGA的硬件实现原理

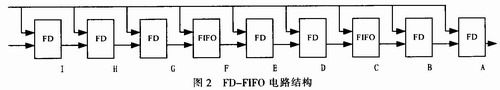

由于双线性插值法需要将图像数据采集成3x3的图像矩阵,系统采用一种由FPGA硬件元器件构成的FD-FIFO模型取图像矩阵。电路如图2所示。

如图2所示,每个移位寄存器FD和先入先出寄存器FIFO左侧上端信号为时钟输入信号(上升沿有效),左侧下端信号为8位的像素信号。图像矩阵的采集流程为:8位的图像信号送到第1个FD,然后经过移位操作从第3个FD存入左边第1个FIFO,存入一行图像数据后,等第2行图像数据送达时,第2行的图像数据经过移位操作从FD存入左边第1个FIFO,同时存储在第1个FIFO的数据开始读出到第4个FD,再经过移位操作存入第2个FIFO,等待两行图像数据都存储后,当第3行图像数据送达至第3个FD,同时后面2个FIFO分别读出前两行的前3个图像数据时,就可以从FD和FIFO的输出端口读取到1个3x3的图像数据矩阵:3x3矩阵第1行从左到右的数据为ABC,第2行的数据从左到右为DEF,第3行的数据从左到右为GHI。

CMOS图像传感器采集的图像大小固定为2 592x1 946x12 bit的Bayer图像,FPGA先用一个12位输入8位输出的移位寄存器取图像的高8位,再利用FD-FIFO得到3x3的图像矩阵,然后可以根据双线性插值法计算图像的RGB信号。双线性插值法虽然算法简单,且易于实现,但是存在边界效应。系统对边界效应做了如下的处理方法:对图像四周全部补零,即先将图像扩展成2 594x1 946大小,然后计算得到2592x1 944大小的图像,这样得到的图像仍是完整尺寸。只需在运算的时候,针对不同四周特殊的像素采用裁减的公式(系统中不产生零像素,只是对计算公式中相应边界

- FPGA构建高性能DSP(01-13)

- PCI-X总线图象处理技术(10-24)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)