基于CPLD+DSP的实时数字图像稳定系统

用"乒乓"结构的数据交换,所以奇场和偶场的起始信号触发EDMA通道中断,虽然传送数据的源地址相同,但目的地址却不同。而C64的EDMA控制器提供了一种称为连接(linking)的传输机制,可以将不同的传输参数组连接起来,组成一个传输链,为同一通道服务。在链中,一个传输结束后,自动装载下一次传输所需要的事件参数。根据这个特点,为每个EDMA通道配置两组参数,用连接的方式完成"乒乓"结构的数据读写。

5 算法程序优化

由于图像处理的数据量大,数据处理相关性高,并且具有严格的帧、场时间限制,因此如何针对图像处理的特点对DSP进行优化编程,充分发挥其性能就成为提高整个系统性能的关键。主要在下面方面的优化方法提高C代码的性能:

1)使用内联函数 C6000编译器提供的内联函数(intrinsic functions)。内联函数是直接映射为内联的C6000指令的特殊函数,可以快速优化C代码。

2)使用字访问短型数据 C6000的内联函数中的某些指令,如_add2()是对存储在32位寄存器的高16位和低16位字段进行操作。当对一连串短型数据进行操作时,可使用字(整型)一次访问2个短型数据,减少对内存的访问次数。

3)人工干预软件流水 流水是用来安排循环指令,并使这个循环的多次叠代并行执行的一种技术,通过线性汇编指令,并行处理数据处理指令。

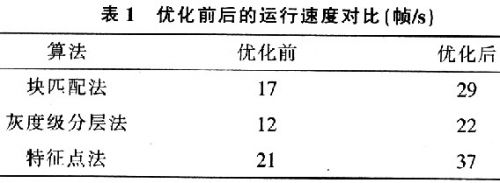

通过以上3种方法优化,程序执行效率提高70%以上,表1中列出各种算法速度做50次运算的平均值。

实际上,在程序优化方面,还有很多的工作可作。另外,本实验室前期开发的基于TMS320C6711型DSP的图像开发板,工作频率在200 MHz,优化后对256×256大小的图像进行10~13帧/s的图像稳定,尚不能达到实时。而基于TMS320C6416的处理板,不优化就能达到18~22帧/s的处理速度,经过简单优化后,如提前进行图像块旋转并读入片内,展开循环,就能达到30帧/s的实时处理。现已移植的算法包括:基于快速搜索的块匹配法、灰度级分层法、边缘匹配法,各种算法都完全能够进行实时运行。

6 结论

该系统通过选用CPLD+DSP,既能保证系统的执行速度,也能保证可靠的逻辑控制。该系统实现一个比较完整的图像采集、传输、处理和送显的硬件实验系统,由CPLD对系统的运行逻辑进行控制,通过对编写在DSP上运行的图像处理程序进行优化后,能够实现大小为512×512像素图像的实时稳定。该稳像系统作为一个独立的图像处理系统,可完成多方面的图像处理功能,也为其他基于DSP的图像处理平台的设计提供了参考。

DSP 实时数字图像稳定系统 CPLD 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)