基于DSP的高速数据采集系统设计方案

引言

近年来,高速数字信号处理器(DSP)已越来越广泛地用于各个领域,例如:通信、语音处理、图像处理、模式识别及工业控制等方面,并且日益显示出巨大的优越性。数字信号处理器是利用专门或通用的数字信号处理芯片、以数字计算的方法对信号进行处理,具有处理速度快、灵活、精确抗干扰能力强、体积小、可靠性高等优点,满足了对信号快速精确实时处理及控制的要求。

通用串行总线USB(Universal Serial Bus)具有连接灵活、可热插拔、一种接口适合多种设备、速度高、自动配置、无需定位及运行安装程序、可为外设提供电源、低功耗、低成本、高可靠性等优点使数据的高速传输变得非常便利。

设计一种通用数据采集与信号处理系统,采用高性能的TMS320F2812 芯片和USB总线传输技术,使信号能实时送到上位机进行分析与处理,从而实现高速的数据采集和处理功能。

1、系统概述

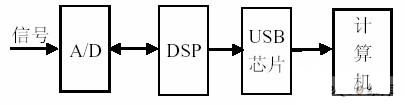

该系统的工作过程主要是将外部的八路同步模拟输入信号经过A/D 转换器进行采样和转换,并把采集得到的大量数据送入DSP 内部对采样结果进行软件滤波以及前端处理。在DSP 完成采集数据的处理工作后,将处理结果经过USB 总线送至主机,进行实时的后端分析处理和显示。

结构框图如图1 所示,MAX1308 为MAXIM 公司生产的模/数转换器,其采样最高速率为单通道1075kSPS,8 通道为456kSPS ,精度为12 位,为8 通道同步采样。采用TI 公司的TMS320F2812 作为处理器,其时钟频率最高为150MHz,是目前控制领域性能最高的处理器,具有精度高、速度快、集成度高等特点,为不同控制领域提供了高性能的处理器。USB 接口芯片采用的是CH372 ,具有8 位数据总线和读、写、片选控制线以及中断输出功能,可以方便地挂接到DSP 控制器的系统总线上。利用VC++ 实现了USB 和计算机的高速数据通信,充分利用了计算机的存储容量大等特点,可将采集到的数据存储起来供事后分析,也可以实现数据的实时处理。

图1 系统框图

2、系统硬件

2.1 TMS320F2812

C281x 系列DSP 是TI 公司最新32 位定点数字信号处理器,是基于TMS320C2000 数字信号处理器平台开发的,其代码与24x/240x 数字信号处理器完全兼容。因此,240x 的用户能够轻松的移植到C281x系列DSP 平台上,C281x 系列DSP 同时具有数字信号处理器和微控制器的特点,尤其是C281x 继承了数字信号处理器的诸多优点,其中包括可调整的哈佛总线结构和循环寻址方式。微控制器的特点主要包括字节的组合与拆分、位操作等。哈佛总线结构能够完成指令的并行处理,在单周期内通过流水线完成指令和数据的同时提取,从而提高了处理器的处理能力。

C281x 处理器采用C/C++ 编写的软件,其效率高,因此用户不仅可以应用高级语言编写系统程序,也能够采用C/C++ 高效率的数学算法。C281x 系列数字信号处理器在完成数学算法和系统控制等任务时都具有较高的性能,这样就避免了用户在一个系统中需要多个处理器的麻烦。C281x 处理器内核包含了一个32×32 位的乘法累计单元,能够完成64 位的数据处理能力,从而使该处理器能够实现更高精度的处理任务。

2.2 USB接口

USB 通用接口芯片可分为3 种。一种是专门为USB 应用设计的USB 芯片,一种是建立在现有芯片系列基础上的USB 芯片,还有一种是只处理USB 通信,必须被一个外部微控制器所控制的USB 芯片。该设计采用CH372属于最后一种。

CH372 内置了USB 通讯中的底层协议,具有省事的内置固件模式和灵活的外置固件模式。在内置固件模式下,CH372 自动处理默认端点0 的所有事务,本地端DSP 只要负责数据交换,所以DSP 程序非常简洁。在外置固件模式下,由外部DSP 根据需要自行处理各种USB 请求,从而可以实现符合各种USB 类规范的设备。

图2 USB 硬件电路图

CH372 与 TMS320F2812 之间以非总线方式连接,连接框图如图2 所示。CH372 的8 位数据口D0 ~D7 分别挂在TMS320F2812 的GPIOA0 ~ GPIOA7 准双向I/O 口上,命令数据地址选择端A0,读信号选择端RD,写信息选择端WR 和中断输出端INT 分别与TMS320F2812的GPIOA9、GPIOA10、GPIOA11 和GPIO8(CAP1)相连,片选引脚CS 接地。

2.3 AD 转换器

该系统采用MAXIM 公司的MAX1308 型号的AD 转换器,MAX1308 独立的采样保持(T/H)电路为每个通道提供同时采样,MAX1308 提供±5V 输入范围,输入故障容限为±16.5V。其ADC 在0.9µs 内完成2 个通道的转换,在1.98µs 内完成多达8 个通道的转换,8 个通道转换时每通道吞吐率为456kSPS。其他特性包括20MHz 的T/H 输入带宽、内部时钟、内部(+2.5V)或外部(+2.0V

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)