基于DSP Builder的脑电信号小波处理

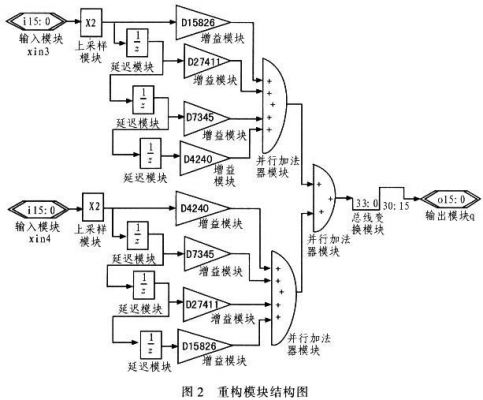

水线方式工作的。二次捕值模块由DSP Builder的上采样模块实现。

4 仿真与设计

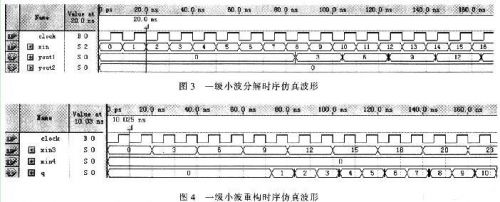

选定一组原始数据[1,2,3,4,5,6,7,8,9,10,11…],同时作为输入信号,利用图1生成的HDL文件,在Quartus II环境下时序仿真,图3为一级小波分解时序仿真波形。利用图2生成的HDL文件,同时把图3低频高频的输出结果作为重构输入数据,进行一级小波重构仿真,仿真波形如图4所示。由图3、图4可以看出,重建后波形除有延迟外,其重建波形无失真,并能完美重构原信号,即输入、输出满足q(n)=xin(n- k)。

利用小波变换的多尺度分解和重构方法滤除信号的某些成分(高频或低频),采用DB2小波对脑电信号进行四级小波包分解,按照小波包分解原理,级联一级分解模块,每经一次分解输入的一串数据降为原来的一半.采用分频模块控制各级时钟信号,分频模块由VHDL语言编写生成.同步输出3个时钟信号,以此作为后三级分解的时钟输入信号。然后对分解后的输出信号进行四级小波包重构,按同样方式处理,级联一级重构模块,每重构一次输出数据都增为原来的2倍。尝试采用锁相环控制各级时钟信号,锁相环由Quartus II自带的功能模块实现,同时输出3个倍频时钟信号,作为后i级重构部分的输入时钟信号。

5 结论

利用信号的小波包分解高分辨率的时频关系.在滤波部分选取因果滤波器对脑电信号进行实时滤波。在DSP Builder平台上,结合Mallat算法和模块化设计原则,设计出基于FPGA的流水线结构小波变换系统,这种自上而下的高度模块化设计方法使得系统的升级改动相当方便,将这种基于FPGA的小波变换系统设计应用于脑电信号的实时滤波,是今后的研究方向。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)