基于DSP的导弹仿真器嵌入式组件设计

2.2.1 中断服务单元

在中断处理周期内完成符合导引头与飞控组件信息交换协议的429信息传输控制,包括429交换信息和遥测信息的实时发送、接收,数据的打包、解包及处理,实现与飞控算法回路的闭合。

中断处理周期是指:利用周期为30ms、占空比为1:1的同步方波信号正负电平产生中断控制信号,来同步信息交换过程。在同步信号的正电平15ms工作周期内,模拟导引头发送20个信息字组成的遥测信息帧。嵌入式组件向遥测系统发送的信息字共有60个。在同步信号的负电平15ms周期内,嵌入式组件与飞控组件完成一帧20个字的信息交换过程。

中断服务单元处理流程如图3所示。429数据接收、发送、数据打包、解包的相关算法模块,限于篇幅这里不再赘述。

2.2.2 时序控制单元

完成导弹正常测试逻辑的控制,包括系统初始化、精确定时,利用DSP的数字I/O资源模拟与其它组件、设备的信息交联,D/A则用来模拟舵偏角反馈信号给设备。其中初始化函数void TargetInit(void) 完成了对DSP、FPGA资源的初始化(中断资源、系统时钟/定时器资源、I/O端口资源、内存等,FPGA缓冲区的清零、寄存器的置位)。函数SetTimerCounter(0)用于系统定时器清零,函数void sleep(unsigned long time)用于系统延时,精度1us。时序测试点的状态判读和信号设置靠对DSP I/O端口资源的读写来完成,在CPLD的逻辑程序SConIO.vhd中定义了信号的端口地址和偏移量。

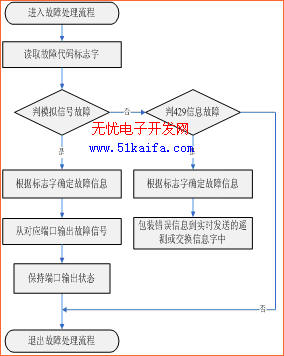

2.2.3 故障测试单元

完成对故障设置装置20余种代码的识别,该单元在流程处理上不是独立的,而是嵌入到时序控制和中断服务单元中,按预定的故障测试流程输出超出设备判别指标的相关错误信息,处理流程如图4所示。

图3 中断服务单元处理流程

图4 故障测试单元流程

3 问题及解决途径

在设计调试中断服务程序时,遇到的突出问题就是系统实时性要求与CPU处理能力间存在的差距。由于系统同步信号中断对429数据传输与处理的时间要求非常严格,特别是15ms负半周,不但要完成数百个包括浮点参数运算在内的数据实时处理,还要管理429数据的接收与发送。象F240这样的定点DSP运算效率显然难以胜任。为此,在设计中断服务程序模块时采取了如下措施:

a) 在中断服务流程中,合理安排CPU查询缓冲区状态的时间点,待CPU将接收到的上一帧数据和待发送的下一帧数据处理完毕后,再查询缓冲区的数据个数,接满后由CPU读走进行处理,从而实现了接收数据与处理数据的并行操作;

b) 数据传输操作主要靠FPGA逻辑程序在后台进行,CPU在前台完成数据处理;

c) 在429参数打包、解包处理过程时,对频繁使用的二进制加权处理方法进行改进,不再调用C标准算法库math.h中的pow( )函数,取而代之自定义的移位运算函数,pow( )是通用的C整型/浮点型运算库函数,F240调用它势必会占用大量的机器周期,而移位操作在实现二进制加权功能的同时,运算速度却能成倍提高。

为证明措施的有效性,使用DL716数字记录仪对DSP两个空闲I/O通道在同步信号正负半周产生的电平反转状态变化进行实时采集测量,得到系统在中断处理过程的耗时见表1(统计了测量6次的数值)。测试结果表明,系统在同步信号中断负半周的运行时间大幅缩短至13.5ms左右,不仅排除了中断和数据帧丢失的可能性,而且满足了信息交换协议对时序控制和数据的处理要求。

表1 中断处理时间对照表

4 结 论

作为嵌入式系统在国防科技领域内推广使用的典型范例,该组件目前已成功应用于某型导弹仿真器中,在各类复杂的使用环境下均显示了良好的性能,对于用户尽快掌握新装备形成战斗力具有非常重要的现实意义。

本文创新点:采用DSP+FPGA嵌入式系统构架,遵循弹载电子设备对于体积和性能的设计要求,同时采取并行处理和软件算法优化等措施,满足了系统对于集成化、功能性、可靠性、实时性的要求。

参考文献:

[1] TMS320F/C240 DSP Controllers Reference GuidePeripheral Library and Specific Devices[M], Texas Instruments, 1999.6.

[2] DDC Data Sheet (DEI1016 ARINC429 Transceiver) [ Z].DDC Inc, 2004

[3] 徐欣,于红旗,易凡.基于FPGA的嵌入式系统设计[M].北京:机械工业出版社,2005

[4] 缪云青,李永刚.FPGA器件在嵌入式系统中的配置方式探讨[J].微计算机信息,2006,11:161~162

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)