基于DSP的导弹仿真器嵌入式组件设计

0 引 言

在某新型机载武器系统的研制过程中,作为确保战备部队尽快掌握新装备形成战斗力的关键因素,需要设计一种能达到测试训练目的的导弹仿真器。而该系统设计的核心任务是开发一套能够模拟产生与弹载飞行控制组件进行同步ARINC-429(HB6096-86)信息交换、发送遥测数据、模拟产生时序逻辑控制信号、设置故障代码并能进行故障模式处理等一系列对产品进行测试训练工作的嵌入式组件。

1 系统框架设计

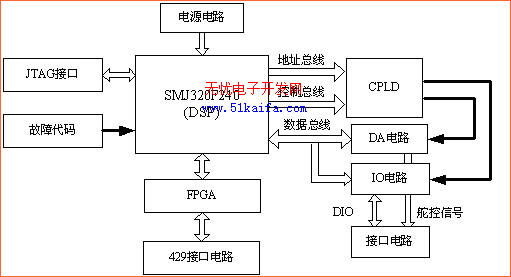

由于该组件为典型的弹载嵌入式系统,使用空间有限、环境条件苛刻,既要求系统运行稳定可靠,又要求具有较强的数据运算能力。综合考虑设计需求,决定采用"DSP+可编程逻辑器件+429通讯接口+信号匹配及调理+故障模拟装置"作为系统的硬件总体框架。限于篇幅,本文只就DSP扩展电路、429通讯接口以及FPGA的逻辑功能加以介绍。系统硬件原理框图如图1所示。

图1 系统硬件原理框图

1.1 DSP及扩展电路设计

选用TI公司98年推出的军品级SMJ320F240数字信号处理器[1],在高效软件算法的配合下完全可以承担嵌入式组件控制处理核心的任务。

SMJ320F240扩展电路包括时钟电路、复位电路、数据存储器扩展电路。SMJ320F240DSP的片内RAM为544字节,为满足系统要求,在计算机板上外扩了32K的DRAM、DRAM采用cycrsj公司的cy7c199-25DMB,容量为32K、8位数据,读出时间为25ns,将两片32K、8位数据存储器拼为32K、16位数据存储器通过72LS00译码电路,将32K16位数据存储器地址空间定为高32K,即8000~FFFF。

1.2 ARINC-429通讯接口设计

就一般的429通讯接口的设计方法而言,通常采用双口RAM作为传输通道的数据缓冲器。但这种设计方法并不适用于本系统。因为上述设计方法只考虑了数据成批的实时传输,即429传输每帧数据均为20×32bit,一般的双口RAM 缓冲区都很大,上下半区可以分别存放很多帧数据并成批的读取,无法实时对每一帧数据进行处理,不符合交换信息协议对每帧数据实时处理这一要求。

针对系统的设计需求,采用新的设计思路,组建以F240、FPGA、DEI1016[2]为构架的智能通讯接口模块。FPGA选用Altera公司的EPF10K20RC208器件,利用VHDL编写逻辑模块来开辟适当缓冲区为数据帧提供实时传送的平台,数据传输操作靠FPGA逻辑程序在后台完成数据的发送接收,CPU则在前台完成数据处理[3]。

数据通讯模块的控制逻辑以F240提供的I/O操作信号IS和读写信号RD、WR以及地址A2、A1为输入来为DEI1016产生操作信号。控制逻辑和F240同时监视DEI1016的RX1RDY、RX2RDY、TX429RDY等3个状态信号以供软件查询和由控制逻辑产生INT中断请求。

1.3 FPGA逻辑设计

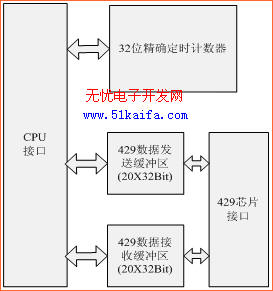

在确定了依靠FPGA大规模可编程逻辑器件作为F240与DEI1016实时通讯的传输环节后,将FPGA逻辑程序划分为5部分进行设计:CPU接口模块、429芯片接口模块、429数据发送缓冲区模块、429数据接口缓冲区模块、32位精确定时计数器模块。逻辑框图如图2所示。

a) CPU接口模块:充当FPGA内部各模块与CPU(SMJ320F240)总线之间的桥梁。CPU把数据总线,地址总线,控制总线挂在CPU接口模块上,CPU接口模块通过地址译码分别选通FPGA内不同的模块与CPU通讯。

b) 429芯片接口模块:主要负责与429芯片DEI1016通讯,DEI1016的数据总线、控制总线连接到这个模块上,该模块根据不同的操作控制DEI1016的控制总线或者响应DEI1016的控制信号,同时通过并行数据总线发送(接收)DEI1016的数据。

c) 429数据发送缓冲区模块:负责接收CPU传过来的待发送的数据和发送启动命令并把这些数据传给429芯片接口模块和启动429芯片接口模块的发送时序。该缓冲区能容纳20个32位数据。

d) 429数据接收缓冲区模块:负责响应429芯片接口模块的接收数据中断信号并把接收到的数据存在内部RAM中,CPU可以通过CPU接口模块查询429数据接收缓冲区已接收的数据个数并且可以随时读取缓冲区中的数据。该缓冲区能容纳20个32位数。

图2 FPGA逻辑设计框图

由此看出,发送429数据几乎是不占机时,将数据放入缓冲区即可。在接收429数据时,该过程完全由逻辑程序在后台运行,不占用CPU的机时,为前后台不同任务的并行操作提供了条件。

2 时序软件设计

2.1 运行环境

在仿真调试阶段软件运行在CCS2000集成开发环境中,使用WinTech仿真器通过JTAG仿真接口在线仿真调试,操作系统为WinXP。在烧录至FlashEEPROM后,软件运行于F240片上系统。

2.2 结构及详细设计

时序软件是嵌入式组件乃至整个导弹仿真器的控制核心,完成对全弹逻辑时序的控制以及对故障的响应。软件工作流程以时序控制为主线实时调度,依次完成系统初始化、故障识别、模拟测试信号的输入输出,同时调用中断服务程序完成与飞控组件的信息交换。软件按模块结构划分为时序控制、中断服务和故障测试三个单元。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)