基于基片集成波导的高增益平面缝隙天线

1 引言

传统的微波无源器件一般由金属波导或微带线构成。金属波导尺寸较大,不能完全适应现代无线通信系统对微波器件小型化、集成化的要求;而微带线功率容量较小,应用场合有限。近年来出现了一种新型的波导结构――基片集成波导(Substrate Integrated Waveguide-SIW),由于它结合了传统矩形波导和微带线的一系列优点而成为国内外学者研究的重点。

本文在基片集成波导的基础上提出了一种新型的平面缝隙天线。天线缝隙采用凹形结构,有效减小了其物理尺寸。该天线工作频率为5.8GHz,结构紧凑,最大增益可达6.9dBi。仿真结果和测试结果吻合较好,从而验证了本文设计的正确性。

2 SIW相关理论

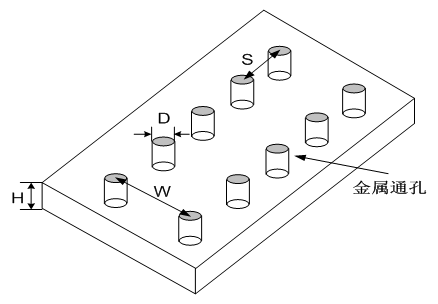

SIW是一种人工集成的波导结构,由两排线性紧密排列的金属通孔或销钉嵌入到上下底面为金属的低损耗介质基片上构成。图1描述了一种典型的单层基片集成波导的结构。图中介质基片的上下表面均为金属,在介质基片中相隔一定距离制作两排金属化通孔,这样就在上下金属面和两排金属化孔之间就形成了一个类似矩形波导的结构。其中基片厚度为H,金属通孔的直径为D,相邻通孔的间距为S,两排通孔的间距为W。通过合理的控制SIW各个单元的尺寸,大部分电磁场可以被限制在两排通孔和上下金属面之间的区域内。SIW具有与金属矩形波导相似的传输特性,因此可以运用矩形波导的相关理论分析SIW。目前主要的分析方法有全波分析法、等效模型法和商业电磁软件仿真等。

基片集成波导具有微带线的许多优点,如体积小、重量轻、便于与微波集成电路集成等。同时还秉承了传统矩形波导品质因数高、便于设计等优点,目前已经广泛应用于滤波器、天线等平面电路中。

3 天线结构分析

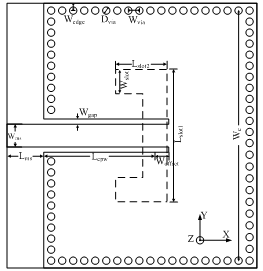

本文建议的平面缝隙天线结构如图2所示。图中介质基片的上下表面均为金属,在介质基片的四周等间距制作一排金属化通孔。通孔的直径为Dvia,间距为Wvia。一般要求Dvia/Wvia>0.5,Wvia/l<0.1。天线的馈电方式为微带线侧馈,50欧姆微带线位于天线的上表面,线宽为Wvia,长为Dvia。缝隙位于介质基片的下表面。天线通过该缝隙向外辐射能量。为了研究平面缝隙天线的性能,本文采用ANSOFT公司的电磁仿真软件HFSS 11.0对其进行仿真设计,同时分析了各个参数对天线性能的影响。

图2 基于SIW的平面缝隙天线结构示意图

3.1 缝隙长度的影响

本文中缝隙采用凹形结构,这样可以缩短天线在Y轴方向的长度,从而有效减小天线的尺寸。通过仿真发现缝隙长度对缝隙天线的中心工作频率和驻波比有明显影响。从图3中可以看出随着缝隙长度的增大,天线的工作频率降低。但是不同的缝隙长度,天线的回波损耗差别较大,一般缝隙的长度为天线工作波长的一半。

图3 缝隙长度对天线工作频率的影响

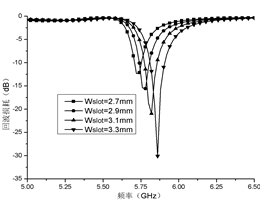

3.2 缝隙宽度的影响

本文中缝隙的宽度为Wslot。图4所示为缝隙宽度对天线工作频率的影响。从图中可以看出随着缝隙宽度的减小,天线的工作频率降低,同时天线的回波损耗也有所增大。

图4 缝隙宽度对天线工作频率的影响

4 仿真和测试结果

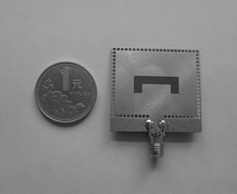

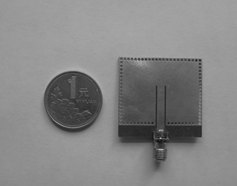

通过软件仿真优化,本文设计的基于SIW平面缝隙天线各个单元的尺寸分别为:Wms=3.1mm, Lms=5.0mm, Lcpw=17.0mm, Wgop=0.7mm, Woffset=1.5mm, Wc=34.0mm, Wedge=0.5mm, Dvia=1.0mm, Wvia=1.5mm。缝隙的尺寸Lslot1=18.0mm, Lslot2=7.0mm, Wslot=3.3mm。板材采用的RT/Duroid 5880,相对介电常数是2.2,厚度为1.0mm。图5所示的是根据上面尺寸所制作的平面缝隙天线的实物图,天线总的尺寸为34 mm´36mm。文中使用安倢伦公司的矢量网络分析仪N5230A对天线实物的回波损耗进行了测试,测试结果如图6所示。从图中可以看出,天线的中心频率为5.8GHz,回波损耗小于-20dB,工作带宽为2%,测试结果和仿真结果吻合的较好。

(a)顶面

(b)底面

图5 基于SIW平面缝隙天线实物图

图7给出了工作在5.8GHz时平面缝隙天线的增益图,其中实线为Fai=0°的增益图,虚线为Fai=90°的增益图。从图中可以看出该天线的主辐射方向位于缝隙所在的半空间,具有半空间辐射的方向性,最大增益可以达到6.9dBi,前后比为-16.4dB,适于应用在微波RFID系统中。

图6 基于SIW平面缝隙天线的驻波图

图7 基于SIW平面缝隙天线增益仿真图

5 结论

本文以SIW技术为基础,利用其品质因数高等优点设计了一款高增益平面缝隙天线。该天线结构紧凑,中心工作频率为5.8GHz,最大增益可以达到6.9dBi,具有