可编程ASIC器件主从式结构开发系统的设计

1 引言

当前在EDA领域,只要具备台式或笔记本电脑并装有工具软件,就可以方便地对可编程ASIC(CPLD/FPGA)进行设计开发,在系统可编程(ISP)器件为我们提供了这种便利条件。ISP方式虽然可以用一根下载电缆代替了编程器,但兼有提供下载和演示环境两大功能的可编程ASIC开发系统对于用户来说仍是必须的。本文提出的主从式下载开发系统可以适配多种目标芯片,具有较宽的开发应用范围,经过几年的教学、科研实践,使用效果良好。

2 系统结构及工作原理

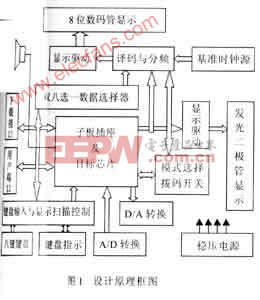

对ASIC器件设计开发的前期工作主要依靠对某种EDA工具软件使用。对于其工具软件和硬件编程语言,必须通过实践锻炼方能熟练使用和达到掌握技巧的程度。对应用系统和目标芯片进行开发,先要使用EDA工具软件所提供的文本和图形输入方式进行描述和综合,并要通过仿真验证。而后的工作就是将设计完成并通过仿真的熔丝图文件对目标芯片下载,并在系统板提供的开发环境中直接进行功能演示。因而下载开发系统的基本结构必须具备输入和输出功能。设计数字电路或系统往往需要多种频率资源,故系统板要提供时钟配置和频率选择功能。而要完成开发系统的复杂工作和模式选择,系统控制功能也是必须的。基于以上思路设计开发的系统电路框图如图1所示。

|

本机最大的特点是系统采用主从式开发结构,将目标芯片安装在一个小型转接板上,再将转接子板插到系统母板上配合工作。主系统母板是固定的,对不同的芯片只需换用不同的转接子板,避免了以往开发系统只能对单一型号芯片进行开发应用的弊端,大大拓宽了目标芯片的可选性和开发系统的应用范围。目前设计的开发系统适用于6000门规模的芯片开发,以及LATTICE、XILINX、ALTERA等多家公司的不同芯片。主从式开发结构保证了系统的通用性和易于升级,只要稍加改进就可形成从2000门到100000门以上逻辑资源、从5V 到3.3V、2.5V、1.8V兼容工作电压的系列产品。

2.2 输出部分

输出部分主要采用数码管显示并有发光二极管显示以及扬声器发声装置。考虑到数码管占用较多的用户资源,我们采用一种动态扫描方式,在输出数码管显示数据时同时输出与该数据相对应的数码管地址,经地址译码器形成数码管选通信号。具体实现时用一片Isp LSI1016可编程器件配置数据选择器和译码器,地址译码功能通过89C51单片机控制实现。这种方案大大节省了输出口资源和译码驱动器件,提高系统可靠性同时减少印板空间。

设计系统具有三种显示模式:准静态显示、十六进制码输入动态显示和段码输入动态显示,用户通过拨码开关或跳线进行模式选择。

2.3 输入部分

采用8键KEY 0~ KEY 7,键盘信号经89C51单片机处理后通过三态缓冲门送至用户芯片,根据不同工作要求,键盘设计有四种输入模式:琴键模式、乒乓模式、脉冲模式和二进制计数模式。除此之外第八键还可为特殊功能做单步时钟输入模式。

2.4 时钟资源及分频

使用ISPLSI1016同时配置时钟产生单元,系统由晶振产生32768 Hz时钟,经1016内部分频可以输出十种频率,这十种频率与另外单独产生的12 MHz信号组合使用(分为四组),可基本满足设计需要。对1016的ABEL-HDL语言描述(包括配置信号源部分的计数、分频和显示部分的译码器、数据选择器)如下:

MODULEdivCLK

TITLE ‘THIS IS THE HEX BITS COUNTER OF BIN BCD CODE TO 7 SEGMENT CODE CODER’

CK PIN 11; “Y0时钟输入”

EN PIN 15; “段码输入使能”

Q0,Q2,Q4,Q8,Q9,Q10,Q11,Q12,Q13,Q14,Q15 PIN 43,42,41,40,39,38,37,32,27,26,10

ISTYPE ‘COM’; “分频器输出”

NQ0,NQ2,NQ4,NQ8,NQ9,NQ10,NQ11,NQ12,NQ13, NQ14,NQ15 NODE ISTYPE ‘REG_D’;

C0,C1,C2,C3,C4,C5,C6 PIN 8,7,6,5,4,3,44 ISTYPE ‘COM’; “最终结果输出”

A,B,C,D PIN 19,18,17,16; “十六进制码输入”

IN0,IN1,IN3,IN4,IN5,IN6 PIN 20,21,22,31,30,29,28;

“段码输入”

CLKIN NODE ISTYPE’COM’;

Q1,Q3,Q5,Q6,Q7 NODE ISTYPE’COM’;

NQ1,NQ3,NQ5,NQ6,NQ7 NODE ISTYPE ‘REG_D’;

QA,QB,QC,QD,QE,QF,QG NODE ISTYPE ‘COM’;

BOUNT=〔Q15..Q0〕; “分频器输出”

COUNT=〔NQ15..NQ0〕;

INPUT1=〔QA,QB,QC,QD,QE,QF,QG〕;

“译码结果输出”

INPUT0=〔IN0..IN6〕; “段码输入”

OUTPUT0=〔C0..C6〕; “最终结果输出”

EQUATIONS

CLKIN=!CK; “该段为计数分频器”

开发 系统 设计 结构 主从 ASIC 器件 可编程 相关文章:

- 嵌入式软件设计中查找缺陷的几个技巧(03-06)

- 基于算法的DSP硬件结构分析(04-02)

- Windows CE下驱动程序开发基础(04-10)

- DSP+FPGA在高速高精运动控制器中的应用(05-17)

- 基于USB接口和DSP的飞机防滑刹车测试系统设计(05-19)

- 一种基于DSP平台的快速H.264编码算法的设计(05-19)