FPGA的TCP/IP通信协议与Matlab通信系统研究

O 引言

近年来,随着信息技术的发展,网络化日加普遍,以太网被广泛应用到各个领域。例如在数据采集领域,一些小型监测设备需要增加网络实现远程数据传输的功能,只要那些设备上增加一个网络接口并实现了TCP/IP协议,就可以方便地接入到现有的网络中,完成远程传输数据的相关功能,所以小型设备的网络技术一直是大家关注的焦点。另一方面,随着单片FPGA的逻辑门数不断增大,人们开始考虑将整个嵌入式系统集成到单片FPGA来实现,于是2001年 Altera第一次提出了可编程片上系统(SOPC)概念,并且推出了第一款嵌入式处理器软核Nios以及之后的第二代Nios II以及相应的开发环境,此后Xilinx也推出了MicroBlaze微处理器软核,之后,随着Altera的CycloneIII和StraTIx IV以及Xilinx的Spartan6和Virtex6等一系列大容量FPGA的推出,Xilinx于2009年正式提出了目标平台设计并且推出了相应的软件ISE 11,至此,嵌入式系统真正开始走向了片上系统,自然,这中间也包括了以太网的嵌入式片上系统。

Matlab是美国MathWorks公司提供的商业数学仿真软件,其中Simulink是Matlab中的一种可视化仿真工具,是一种基于框图的设计环境,可以实现数据的仿真和处理,它提供了一种快速、直接明了的方式,用户可以实时看到系统的仿真结果并且进行相应的数据处理。基于以上事实,本文提出了基于FPGA的嵌入式以太网与Matlab通信系统的设计和研究,采用Xilinx公司的MicroBlaze嵌入式微处理器软核,利用它和相应外设IP核一起完成SOPC的设计并且完成与Simulink数据的传输,最后动态显示以太网传输的数据。

1 系统硬件平台设计

1.1 系统总体硬件的结构

在系统硬件结构中,考虑到系统复杂度和成本因素,我们选用了Xilinx公司的Spatan3A系列的XC3S700A作为主控制芯片,该芯片为Xilinx的Spartan系列的低端FPGA,采用了65nm技术,在集成度和性价比上都要优于先前Spartan系列的FPGA,系统外挂一块 Micron公司的32M×16bits的DDR2芯片MT47H32M16作为外扩SDRAM,以及一片Numonyx公司的16Mb的SPI Flash M25P16作为数据存储器,而10/100Mb以太网我们采用单片PHY芯片加Xilinx的MAC软核来实现。该方案将物理层和MAC分开,将MAC 用IP来实现,从而整个系统更加灵活。其中单片PHY芯片有BroADCom公司的BCM5221,Intel公司的LXT971A、 LXT972A,SMSC公司的DM9000、LAN83C185等。这里我们采用SMSC公司的LAN83C185来实现物理层。

1.2 系统整体框图

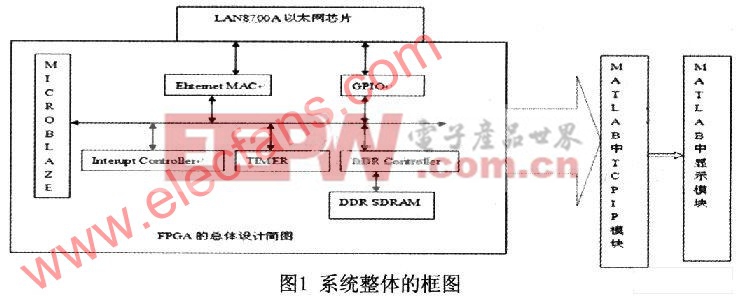

虽然Matlab中可以采用相关命令创建一个TCP/IP的模块进行数据的接收和显示,但是与Simulink中TC/IP模块相比较为繁锁,因此选择用后者动态实时显示从以太网发送过来的数据,并可进行相应的处理。本设计主要是完成发送正弦函数数据并在Simulink的接收模块中显示正弦函数图形。系统的整体的框图如图l所示:

2 MicroBlaze的系统硬件配置和Simulink接收块的搭建

2.1 MicroBlaze和系统设计

Xilinx公司的MicroBlaze嵌入式软核是业界优秀的32位软处理器IP核之一,它支持CroConnect总线标准设计集合,具有兼容性和重复利用性,最精简的核只需要400个左右的Slice,MicroBlaze软核内部采用哈佛结构的32位指令和数据总线,便于各个外设和它们之间的信号传输及相应的控制,它有下面的几种互联总线:

(1)处理器本地总线(PLB)。可以将多个PLB主设备和PLB从设备连接到整个的PLB系统中。

(2)高速的本地存储器总线(LMB)。用来取RAM块的同步总线。

(3)XCL总线。是一个高性能的外部内存访问总线。

(4)FSL总线。用于点对点的单向通信总线。使整个系统的软硬件设计,包括系统硬件平台的搭建,驱动程序的配置,Xilkernel操作系统内的核参数配置,软件库的设置,文件系统的生成及外设控制芯片接口配置都可以在EDK(Embedded Development Kit)内完成。EDK的整体开发流程如图2所示。

整个系统设计具体操作如下:

(1)在EDK的集成开发环境XPS(Xilinx Platform. Studio)中,处理器功能单元,系统外围总线结构,终端外设以及相应的地址映射和默认的驱动等都可以在BSB(Base System Builder)中完成。在Microblaze系统的基本构建中其主要设置如下:使用Single Processor System系统,Local Memory为16k,系统时钟频率为62.5MHz,定时器和以太网中断必须连接到处理器的中断控制器上,另外,本设计还用到的GIOP、 Ethernet MAC、DDR、SDRAM控制器等,其间用到的IP驱动,都是用xilinx提供IP的自带默认的相应驱动。

(2)最后XPS自动生成微处理器硬件规范MHS(Microprocessor Hardware SpecificaTIon)和描述软件系统结构的微处

FPGA 软核 嵌入式 外设 动态显示 片上系统 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)