FPGA的TCP/IP通信协议与Matlab通信系统研究

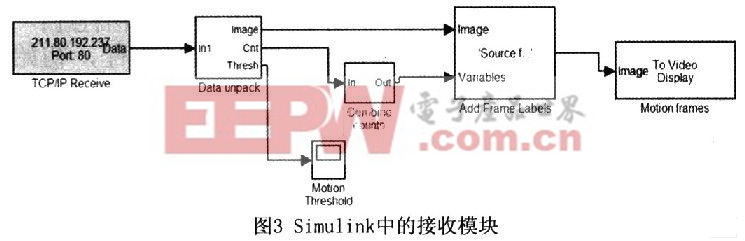

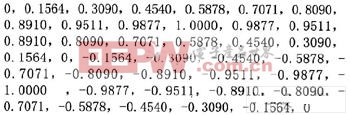

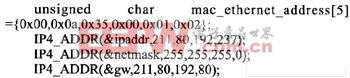

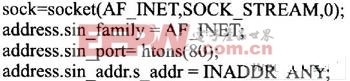

理器软件规范MSS(Micro-processor Software Specification)文件以及一些相关的文件。这些文件都可以手动进行修改,从而是使整个系统更加的优化。 (3)生成的系统最后生成bit文件,把其文件下载到目标板子上。 2.2 Simulink接收模块的搭建 Simulink中TCP/IP中的接收模块,其终端的地址,端口的设置要与FPGA上的以太网的IP地址、端口的设置一致,这就为 TCP/IP接收模块指定了要通信的地址即完成了接收模块TCP/IP的相关配置,也就完成了FPGA与Matlab中以太网通信的接收模块的搭建,在 Simulink中,具体的模块设计如图3所示。 通信数据通过此模块可以较直观地用图形动态显示。 3 系统的软件平台及网络协议的实现 3.1 软件内核和协议 本设计主要选择了Xilinx公司的精简嵌入式操作系统Xilkemel,它是Xilinx提供的用于EDK系统的小型、模块化的嵌入式操作系统内核,它支持Microblaze核,与EDK形成的硬件系统无缝连接,具有可定制、CPU资源占用较小、运行速度快等特点,是MicroBlaze嵌入式软核的理想操作系统,其整体的开发流程如图4所示。 网络通讯协议我们采用TCP/IP协议,该通讯协议采用四层(应用层、传输层、互连网络层、网络接口层)层级结构,每一层都呼叫它的下一层所提供的网络来完成自己的需求,系统分为两部分实现: 第一部分为物理层和MAC层,本设计中用LAN83C185来实现物理层,MAC层由Xilinx公司的Ethernet MAC IP核,并作为整个MicroBlaze系统硬件的一部分在FPGA内实现。 第二部分是运输层和网际层,主要由软件代码实现。TCP/IP网络通信软件允许用户远程注册到另一个系统中,并从一个系统复制文件到另一个系统,虽然Xilkernel本身不带有文件处理系统和TCP/IP协议栈,但它与Xilinx公司的LwIP库具有良好的接口,加上系统支持库 LibXilMFS可形成一个比较完整的嵌入式系统,其特点是内核配置功能都已集成到EDK工具中,使用简单、方便,内核启动静态创建线程,而动态分配内存,可加载或卸载不同功能模块来实现内核的高扩展性。 本设计主要采用LwIP3.OOb(Light weight Internet Protocol stack)协议模块套用于嵌入式系统的开放源代码TCP/IP协议栈中,LwI-P3.00b提供二种API模式:Socket模式和RWA模式,由于 Socket模式开发难度不大,只要启动Xemacif input thread线程,从中断响应的过程中接收数据包并转移到LwlP的tepip thread中就可以。所以基于方便考虑我们决定上层协议部分协议模块采用Socket模式,因此需在MSS文件里对LwIP进行例化(包括相应的 LwIP参数设置)从而减少存储器利用量和代码编写。 3.2 网络通信程序的实现与设计 网络通信程序主要完成从超极终端发送数据,传到Simulink中的ICP/IP接收模块。下面是主要的网络通信程序: Server_thread()函数是Xilkernel的第一个线程,初始化LwIP协议栈。 ServerAppThread()函数可完成MAC、IP、掩码以及网关的配置,并完成Socket应用。 以太网的配置如下: -- 2010/7/10 23:03:27--> 当服务器程序开始运行时,主进程就创建一个套接字, 并通过bind函数绑定,用函数listen进行*,之后用lwip_accept进行接收,然后用sys_thread_new启动进程,processGet和Process Command函数分析数据包的内容并应用web serber定义的相关的命令实现相关的应用,write函数实现数据的发送,完成Socket服务并把数据发送给客户端。 Simulink中用TCP/IP模块,remote address参数设定为(211、80、192、237),端口设定为80,即与IP4_ADDR(&ipaddr,211,80,l92,237)和 address.sin port="htons"(80)设为一致,这样就保证了接收与发送网络地址和端口的一致性,保证数据传输的可实现性。设计发送的数据为:t=0:0.25:10,Y=sin(2*pi/10*t),数据列表如下: 对应的Simulink接收模块的数据图形显示如图5所示。 由图5我们可以看出,接收到的数据和发送的数据基本一致。 4 结论 本文研究了TCP/IP通信协议在Xilinx公司FPGA上的实现,介绍了其软硬件的系统组成及原理,通过建立一个例子加以说明和应用这个设计平台,证明了此平台设计可行性,并且完成了FPGA与Matlab的通信,为数据的实时显示及实时控制提供了很好的平台和设计方法,本设计也完成了 CPU软核设计的实现,其功能可根据需要进行定制,非常灵活,不但引入了软核处理器和嵌入式操作系统Xilkernel,而且应用了Lw-IP_300b 栈,使用大量的IP核,这样大大降低了系统平台的复杂度,缩短了开发的周期,其软硬件部分的设计分离的设计架构,使得整个系统修改和重构更加方便,真正实现了所谓的片上系统。而本设

FPGA 软核 嵌入式 外设 动态显示 片上系统 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)