利用FPGA实现的任意波形发生器的研究设计

时间:12-28

来源:互联网

点击:

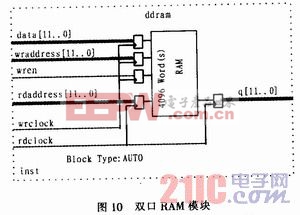

出的高12位),寻址空间为4 K(4 096)个单元,即RAM存储空间应为4 096x12 bit=49 152 bits,由于本设计所选择的FPGA内部RAM最大可配置为119 808 bits,完全可以满足49 152 bits的RAM空间设计。所以波形RAM设计为字长12位,地址线12位。针对任意波形发生器与普通DDS的不同,波形RAM的设计主要要求RAM具有读写两个端口,这样可以通过两套地址系统,方便地进行RAM内容更新,即对RAM的写操作;波形幅度量化数据的输出,即对RAM的读操作。结合ALTERA公司FPGA的特点,选择了EP2C5F256C6这个芯片内部的双口RAM来实现这个功能,如图10所示。 芯片内部的双口RAM具有读地址和写地址两组地址线,数据线也分成了读数据线和写数据线两组。这样波形RAM的设计就非常简单了,将写数据线、写地址线和单片机的数据线、地址线相连,用单片机更新RAM中的数据;将读地址线和读数据线分别与相位累加器的输出和DAC的数据输入相连,读数据线上即输出了波形幅度量化数据。 2 结束语 本文详细阐述了产生任意波形数据和基于FPGA的硬件设计部分,以QuartusⅡ8.O软件平台作为开发工具,选用CycloneII系列的EP2C5-F256C6 FPGA芯片实现DDS结构中的数字部分,其中相位累加器是DDS的核心部件,重点阐述了相位累加器部分的设计,采用8级流水线结构借助前5级的超前进位模块,编译的最高工作频率,由317.97 MHz提高到336.7 MHz,采用此种设计方法,节约了成本,缩短了开发周期,具有可行性。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)