利用FPGA实现的任意波形发生器的研究设计

波形发生器广泛应用于电子电路、自动控制和科学试验领域,是一种为电子测量工作提供符合严格技术要求的电信号设备,和示波器、电压表、频率计等仪器一样是最普通、最基本也是应用最为广泛的电子仪器之一,几乎所有电参量的测量都要用到波形发生器。随着通信、雷达的不断发展,对信号源的频率稳定度、频谱纯度、频率范围和输出频率的个数以及信号波形的形状也提出越来越多的要求。不仅要求能产生正弦波、方波等标准波形,还能根据需要产生任意波形,且操作方便,输出波形质量好,输出频率范围宽,输出频率稳定度、准确度及分辨率高,频率转换速度快且频率转换时输出波形相位连续等。可见,研究制作高性能的任意波形发生器十分有必要,而且意义重大。

1 任意波形发生器的FPGA实现

系统框架如图1所示,上位机产生任意波形数据,经USB2.0控制器CY7C68013A与FPGA(现场可编程门阵列)相连。将数据下载到FPGA的RAM当中,再通过硬件电路依次从波形存储器中读取出来,经D/A转换及滤波后得到所需信号波形输出。

![]()

关于DDS的基本原理与结构在这里就不再加以阐述,用FPGA按照DDS的基本原理和结构设计和实现一个任意波形发生器,所以DDS的几个基本部分都是应当具备的。实现任意波形发生的关键在于把存放波形量化表的ROM换成了可以改写的RAM,这样通过与RAM的接口可以改变存放在波形RAM中的数据从而实现任意波形发生。这里主要介绍控制部分、相位累加器、波形RAM几个模块来叙述任意波形发生器的实现。

1.1 控制部分

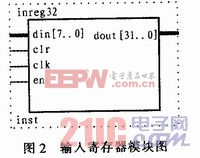

这个部分主要是要解决DDS模块与单片机的接口问题。在FPGA的实现中,主要设计了2个模块,一个是输入寄存器模块,为了接收单片机写入的频率控制字。另外一个是地址分配模块,这样单片机就可以通过不同的地址来选通FPGA各个模块工作。设计中DDS采用了32位的相位累加器。这样对于一个频率控制字,单片机要分4次分别写入4个字节;基于这样的要求,设计了输入寄存器模块如图2,这个部分主要是要解决DDS模块与单片机的接口问题。

din[7..0]是该模块与单片机数据线的接口,clr是低电平异步清零,en是高电平使能,elk为数据写入时钟,dout[31..O]是寄存器输出的32位频率控制字。该模块工作过程为:当en为高电平,clr也为高电平时,elk的上升沿将输入的8位数据锁存进该模块中,当锁存完4个字节的数据后,自动将该4个字节的数据按照先写入的在高位的顺序组合成一个32 bit的数据输出到dout[31..0]。

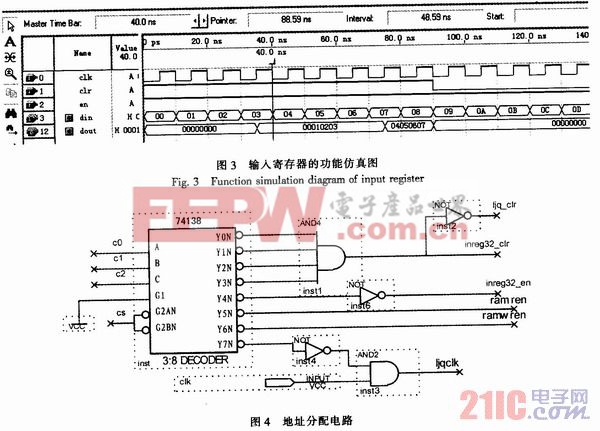

该模块的功能仿真图如图3所示,看到当clr=‘1’并且en=‘1’时,经过4个时钟,dout上将前4个时钟的值‘00’、‘01’、‘02’、‘03’组成32位的‘00010203’数值输出在dout上。

地址分配模块采用一个3/8译码器来实现地址选通的功能,如图4所示。

由于累加器的清零是当“clr”=1的时候,所以在与门后加一个反相器,而频率寄存器清零的条件是“clr”=0,所以,就可以直接与门后相连即可。3/8译码器的使能端接VCC,G2AN和G2BN连起来接CS,作为整个任意波形发生器模块的片选信号,当低电平的时候选中,各模块才开始工作。

地址锁存模块主要解决单片机P0口的分时复用问题。本设计选用的单片机为51系列单片机,其PO口既作为数据口,又作为地址总线的低8位,因此在使用时,需要将地址信号从分时复用的地址/数据总线中分离出来。本设计选用8D锁存器7415373来作为地址锁存器。当74LS373用作为地址锁存器时,应使OEN为低电平导通输出,此时,锁存使能端G为高电平时,输出Q1~Q8状态与输入D1~D8状态相同;当G发生负跳变时,输入端数据D1~D8锁入Q1~Q8。因此在使用74LS373时,51单片机的ALE信号可以直接与74LS373的G相连。

1.2 相位累加器设计

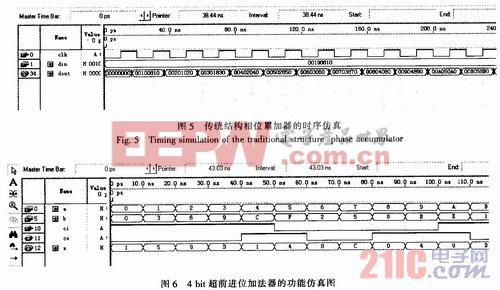

相位累加器用于对输入频率控制字进行累加运算,输入频率控制字决定输出信号的频率和频率分辨率。因此相位累加器是整个DDS性能的关键部分。传统的相位累加器是用1个加法器加1个D触发器组成,调用其中的1个宏模块设置成32位数据相加,再加另一个32位的宏模块,就可以组成相位累加器。它在QuartusII软件中的最高编译频率只有262.12 MHz,显然不能满足设计要求。其时序仿真如图5所示。

通过仿真,当直接采用32 bit累加器的时候系统时钟最大只能达到大约25 MHz,显然是达不到要求的。从设计上看,它实质上是一个带反馈的32位加法器,把输出数据作为另一路输入数据和从单片机传来的频率控制连续相加,产生有规律的32位相位地址码。一般位数小的累加器可以通过FPGA中的进位链得到快速高效的电路,但是进位链必须位于临近的LE(逻辑单元)或LAB(逻辑阵列

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)