面向对称多核体系结构的FPGA仿真模型

MASA流处理器作为计算节点。为更好地验证仿真模型,流处理器中采用功能裁剪的cluster,如图4所示,cluster中仅包含3个计算单元和1个I/O单元,并相应降低指令和数据存储器的容量。在仿真系统中,VAU中的processor为流处理器中的核心计算部件,context backup代替了片上存储部件,其容量为SRF的p倍。该实验的目的是分析所提出的仿真模型对仿真系统的硬件资源消耗和仿真速度的影响。

3.1 资源消耗分析

图5是目标系统和仿真系统的FPGA资源消耗统计。由于布局布线的需求,FPGA芯片的资源使用率最高通常只能达到70%~80%。图5中“×”标识表示当前配置超出EP2S180的仿真能力。可以看出,在不采用仿真优化技术时,EP2S180可仿真的最大规模目标系统为24个计算节点。基于本文的仿真模型,当p值等于4时,EP2S180的仿真能力提高至64个节点;当p值等于8时,其仿真能力提高至96个节点。当p值增大时,其仿真能力可进一步提升。实验结果表明,本文提出的仿真模型能够增大FPGA芯片可仿真系统的规模。

3.2 仿真速度分析

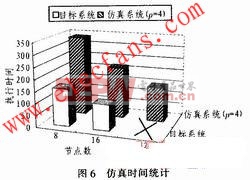

本文采用矩阵乘运算,分别在8、16、32个节点的目标系统和仿真系统上执行,测试二者的仿真速度。目标系统和仿真系统的工作频率为75 MHz。图6展示了二者的执行时间。

可以看出,仿真系统的执行时间大于目标系统。其时间增量主要是由于仿真系统将目标系统中多个processor并行处理的任务移植到一个VAU上串行执行造成。仿真系统没有改变目标系统的数据传输路径和模式,因此,数据传输的时间并没有增加。另外,由于VAU虚拟的p个pro-cessor共享了存储空间,仿真系统中消除了p个processor之间的数据传输时间。虽然仿真系统相对于目标系统执行时间有所增加,但其时间增量处于秒级。相对于缓慢的软件模拟器,并综合考虑仿真模型对FPGA仿真规模带来的好处,因此认为该仿真模型带来的仿真时间增量是可以接受的。

4 结束语

本文提出了面向对称多核体系结构的FPGA仿真模型,以及基于该模型的多核/众核、SIMD体系结构的执行模式。相对于软硬件联合仿真方法,该仿真模型减少了软硬件协同逻辑并避免了设计复杂的软件划分算法。实验结果表明,面向对称多核体系结构的FPGA仿真模型能有效地减少仿真系统FPGA资源的需求,增大FPGA的仿真规模,并且其带来的仿真时间增量是可接受的。但该仿真模型主要是面向对称体系结构,而不适用于异构多核系统等非对称结构。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)