嵌入式机载视频输出接口设计

摘要:针对视频接口接收视频格式单一的问题,设计了一种多格式视频输入接口的视频编码模块。由于采用CH7024视频编码芯片,所以在接口即可接收RGB565和RGB666格式的视频信号。在Linux环境下,对芯片寄存器和视频格式进行配置,编译芯片驱动程序,通过超级终端下栽到芯片中,通过CH7024编码芯片将不同格式的输入信号统一转换成CVBS视频的信号输出,这样可减少电路的硬件设计,并通过对软件的修改来接收不同视频格式的信号。实验结果表明,设计的模块能够适应多种视频格式的信号,且编码后的CVBS视频信号输出距离远,抗干扰性强。

关键词:嵌入式Linux;视频编码;视频输出;驱动程序

0 引言

在无人机视频采集系统中,对于视频信号的要求比较高,采集到的模拟视频信号在ARM9处理器中经过A/D转换,视频压缩编码后通过无线传输到地面基站,通过视频编码芯片将数字信号转换为模拟信号,输出到显示设备上。由于目前数字视频具有多种格式,然而,普通的视频编码模块的输入接口比较单一,不能很好地兼容多格式的视频输入信号,故输出的模拟信号抗干扰性和传输距离都不是太好。

针对上述问题,本文提出了一种基于Freescale的MX27处理器,以Linux 2.6.19为内核操作系统的多格式视频输入编码模块设计方案。硬件方面,以CH7024为主芯片进行电路板设计;软件方面,在Linux环境下,根据芯片的特点,编写相应的驱动程序和寄存器配置。通过加载驱动程序,将不同格式的数字视频信号转换为CVBS复合视频信号,相比其他的模拟视频输出信号,CVBS复合视频信号将亮度、色度、同步和色彩脉冲信息整合到一根电缆内,具有传输距离远,抗干扰能力强等优点。

1 设计方案

1. 1 系统硬件结构

硬件连接如图1所示,将MX27中LCD控制器输出的标准数字视频信号(包括像素数据LD[17:0]、像素时钟LSCLK,行同步信号LP/HSYNC、场同步信号pLM/VSYNC,数据使能信号ACD/OE)接入CH7024的数字输入接口。此外,将MX27中I2C控制器的SPC,SPD线直接与CH7024相应的信号线连接。

1.2 视频输出接口设计

由于以前的芯片输入数据只有16位,接口兼容性不好,而选择的CH7024有24位视频数据信号线,可接收不同的数据格式,包括RGB和YC-rCb(如RGB565,RGB666,RGB888,像ITU656的YCrCb),可接收24b/18b/15b/12b/8b等多路复用数字输入。为了能在系统运行出现故障时方便地进行复位,设计中添加了人工复位电路,这也是以前芯片所没有的。应用CH7024芯片设计的编码器,具有很好的兼容性和通用性,所以选择用CH7024主芯片进行设计。

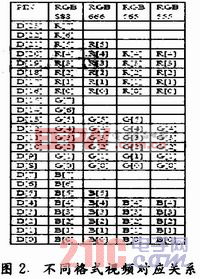

CH7024视频编码芯片的输入接口最多能接收到的视频信号位数为24位,输入格式为RGB888。这样RGB每个通道用8 b来表示,但是对于RGB 666和RGB565等格式的视频信号就涉及到每个通道用几位来表示某个颜色的问题。对于RGB666来说,每个通道用6b来表示;对于RGB565来说,R和B每通道用5 b表示,G通道用6 b表示。对于RGB666和RGB565格式的视频信号,在设计中芯片上的24位数据线分配情况如图2所示。通过对相关寄存器的配置,实现对不同格式视频信号的接收,使其具有较好的兼容性。该方案是以MX27处理器为平台进行设计的,MX27输出的视频信号为18位数据,这样MX27处理器发出的RGB666和RGB565格式的视频,都能通过该方案设计的编码器进行编码。

2 视频编码器软件设计

2.1 I2C总线

I2C总线是一种两线式串行总线,用于连接微控制器及其外围设备。由于接口直接在组件之上,因此I2C总线占用的空间非常小,减少了电路板的空间和器件引脚的数量,降低了互联成本。I2C总线可支持多主机控制,其中任何能够进行发送和接收的设备都可以成为主控端。

I2C总线的串行总线由数据线SDA和时钟SCL构成,可用于发送和接收数据,并可在CPU与被控IC之间、IC与IC之间进行双向传送。在数据传送过程中共有3种信号,分别是开始信号、结束信号和应答信号。其中,开始信号是在SCL为高电平时,SDA由高电平向低电平跳变,开始传送数据;结束信号是在SCL为低电平时,SDA由低电平向高电平跳变,结束传送数据;应答信号是接收数据的IC在接收到8 b数据后,向发送数据的IC发出特定的低电平脉冲,表示己收到数据。CPU向受控单元发出一个信号后,等待受控单元发出一个应答信号,CPU接收到应答信号后,根据实际情况判断是否继续传输信号。若未收到应答信号,则认为受控单元出现故障,如图3所示。

2.2 视频数据的传输

在该设计中,视频数据经过MX27处理器后转换为RGB输送到LCDC中,通过CH7024输入接口接收数据,数据传输的方式如图4所示。当场同步信号(VSYNC)产生低电平时,说明新的一帧数据需要采集,这时采集到的是有效视频信号;当场同步信号再次产生低电平时,一帧数据采集完成,等待进入下一帧数据的采集。在场同步信号之间有n行数据,现以其中一行数据来分析,只要开始采集和采集完一行数据就会产生行同步信号(HSYNC),当行同步信号产生低电平时,说明要采集的一行为有效数据,在等待中断采集;即当OE为下降沿时,开始采集一行数据;当OE变为上升沿时,一行数据采集完毕。图中给出的LINE[1:n]是说一帧图像有n行,每行有m个像素,也就说一帧图像的大小为n×m。

- μC/OS-II下通用驱动框架的设计与实现(07-23)

- 基于S3C44B0X+μcLinux的嵌入式以太网设计(07-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)

- DSP和Flash接口技术的实现(08-15)

- dsPIC33F系列DSC的 SD存储卡接口设计(01-05)