FPGA电路动态老化技术研究

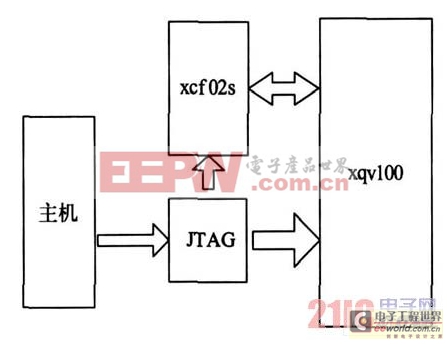

Mbit。 FPGA电路动态老化板采用400mm×400mm的双层PCB板,在设计老化板时采用去耦及高、低频RC滤波,对直流电源和信号源采取限流措施。每块老化板上设计4个老化工位,为了便于在线调试电路,每个工位由一个XCF02S、一个JTAG 接口、一个XQV100 组成。FPGA芯片动态配置的逻辑程序放置于xcf02s Flash存储器中。FPGA动态老化的配置程序采用VHDL语言编写,采用ISE(V9.1)工具进行综合,利用ModelSim(V6.0)进行功能模拟,其具体功能是把全部输入、输出管脚分五组,每组都实现32 分频功能,每组由外部提供一个1MHz 的方波信号作为输入。计算机通过Xilinx 专用的JATG下载线将编译过的配置程序下载到xcf02s 电路中。当FPGA电路上电时,xcf02s 中的配置程序自动按照串行的方式下载到FPGA的内部RAM存储器中,FPGA 按照程序的功能运行。每个电路选择一个输出端口,输出频率在1Hz 左右,在外部连接一个LED灯作为输出监控,在老化的过程中可通过该灯观察电路是否正常工作。 6 结果与分析 我们以XQV100 型FPGA电路为例,进行动态老化和静态老化对比试验,试验条件选择温度为125℃,时间160h。随机抽样60只常温测试合格电路,各取30只分别按照动态老化试验方法和静态老化试验方法进行老化。在动态老化通电时,确保每只电路都有输出;静态老化试验时,确保电源电压输入正确。每1h记录一次,确认是否有老化异常情况。 电路在经过26h 后,其中有1 只(6#)电路LED不闪烁,初步怀疑已经失效,但并没有立即取出,和其他电路一样经过160h老化,经过126h 后21# 电路的LED 不闪烁,同样继续陪试。在老化试验结束后96h内完成了所有电路的常温电测试,发现6# 和21#电路功能失效,其余电路都合格,具体情况详见表1。 表1 动态老化和静态老化比对试验结果 动态老化试验方法和静态老化试验方法相比,动态老化试验在通过外围配置电路的程序驱动,使电路的内部功能模块一直处于高速的工作状态,相反静态老化时虽然有电压加载,但没有配置程序驱动电路工作,内部模块并一直处于空闲状态,因此FPGA电路在动态老化时,所受到的应力条件更加严酷,更容易暴露电路本身潜在的缺陷,从而提高了电路本身的可靠性。 7 结束语 目前,国内进行FPGA电路的老化大部分还是采用静态老化试验方法。特点是电路老化时不工作,内部门阵列不翻转,老化过程中无法判断电路是否有异常。FPGA电路动态老化试验方法的实现解决了这些问题,增加了输出监测点,保证了电路老化过程无异常,从而提高了电路的可靠性。 本文通过对FPGA 电路加载配置过程的流程和原理进行研讨,设计了FPGA 电路动态老化的试验方法,并在工程实践中得到了成功的实现和运用。 虽然这里设计的电路和配置过程针对Xilinx 公司的Qpro Virtex Hi-Rel系列XQV100电路,但是对其他系列和其他公司FPGA的动态配置也有参考作用。本方法虽然实现了动态老化的目的,但还是存在着缺陷:现有FPGA电路的内部门数已经超过了100万门,一般的配置程序只能占用FPGA 电路的部分内部资源,并且用到的D 触发器多了,则移位寄存器就少,通常是顾此失彼,因此要做到100%的动态老化试验还存在着一定的困难。

FPGA XQV100 Virtex 老化 xilinx 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)