基于FPGA的语音信号实时处理

摘 要: 介绍一种在语音识别系统中运用FPGA技术对语音信号进行前期实时处理的方法。利用DSP Builder设计信号处理算法的图形化电路模块,运用硬件环(HIL Hardware in the Loop)技术对模块进行软硬件协同仿真。满足设计要求后,再用Signal Compiler 将模块转换成VHDL语言和Quartus II工程文件下载至目标芯片。结果表明此方法可以快速灵活地设计出语音处理模块,语音数据能在要求的时间范围内处理完毕,达到了实时处理的目的。

关键词: 语音识别; FPGA; 实时; 信号处理

随着语音识别技术的应用越来越广,对其实时性的要求也越来越高。专用的DSP语音芯片虽然有硬件加速功能,但其指令依然是串行计算,在实时性方面有所欠缺。如今,具有并行运算能力的FPGA主频不断提高,加上其设计灵活、功耗低、体积小等优点[1],可以满足语音信号实时处理的要求。目前很多语音处理算法都是基于软件平台的,真正的语音处理硬件实现很少。本文针对非特定人的语音信号,研究当前主流的语音处理算法,并将这些基于软件平台的算法“硬件化”。在保证一定精度的前提下将浮点运算转换成便于FPGA实现的定点运算[2]。

本文以通过对语音信号滤波、分帧、加窗、能量计算等模块的设计为例,介绍语音信号实时处理的方法,需要运用到MATLAB.、DSP Builder、QUARTUS II、ModelSim等EDA工具联合设计[3]。语音信号经过模数转换进入FPGA以后,对其滤波,因为要对信号进行实时处理,需要采用动态分帧,最后计算出每帧的能量为语音信号的下一步处理如端点检测、特征提取[4]等做好前期准备。

1 实时处理算法分析

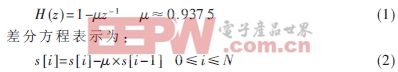

语音数据经过A/D转换之后进入芯片,首先对其进行滤波。为了使信号的频谱趋向平坦,需要对其进行预加重滤波,这里采用一阶FIR滤波器[5]:

语音信号虽然是一种非平稳信号,但在短时内(10 ms~30 ms)可以看作是平稳的[2],这样就可以对其进行分帧处理。在实时系统中无法确定语音的长度和大小,只能对其进行动态分帧。考虑到帧的连续性,采用交叠分帧,帧移取0.5,硬件中可以用两个FIFO实现,其中FIFO1的读时钟频率是写时钟的两倍,且FIFO2的读写时钟频率与FIFO1读时钟频率相同。

分帧后的数据需要窗函数对其加权,加窗后的语音信号为sω(n)=s(n)×ω(n)。由于汉明窗在语音频段的平滑特性,因此本文采取汉明窗[4]:

2 硬件模块的实现

仿真时通过读取hex文件来模拟实时的数据流。通过MATLAB将采样频率16 kHz,宽度8 bit的wav格式音频文件转化成hex文件的数据。部分代码如下[6]:

……

[y,fs,n]=wavread(‘speech.wav’);

y1=int8(y×(2^n-1)+128);

[a,b]=size(y1);

fid=fopen(‘speech.txt’,’wt’);

for i=1:a;

line=[num2str(i-1),’:’,num2str(y1(i)),’;’];

fprintf(fid,’%s\n’,line);

end

fclose(fid);

……

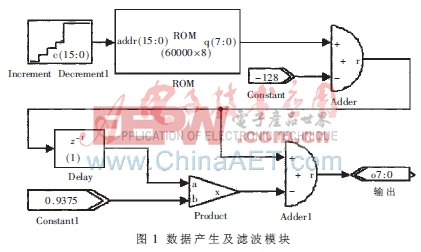

在模块中通过地址计数器将ROM中的数据不断读出,然后对数据流进行滤波。其DSP Builder模块实现如图1所示。

考虑到语音信号的短时平稳性,将256点数据分为一帧写入Dual-Clock FIFO,写入128点后以两倍的写入速度读出,同时以两倍速度写入深度为128的FIFO2。如此循环便可以实现帧的交叠。具体实现如图2所示,左半部分为时钟控制模块。

为了使每帧的数据点与窗函数的数据点一一对应,在加窗之前搭建了一个时序控制模块。Constant1控制模块延时384个时钟周期,counter是模为256的计数器。将LUT设为17 964-15 073×cos([0:2×pi/255:2×pi])[6]。分帧后的信号取模然后与窗函数相乘再累加便得到其能量,由Multiply Accumulate模块实现[2]。Clock提供基础时钟,PLL产生模块所需要的两个时钟,Signal Compiler对模块进行编译,转化成VHDL语言。具体模块如图3所示。

3仿真测试

将上述三个子模块和Simulink中的模拟示波器Scope连接在一起,读取ROM中语音”1、2、3”的数据流。结果显示在示波器上,如图4所示。从上到下依次为原始信号、滤波信号、分帧信号、能量信号。

从图中可以看到设计模块已经可以实时处理数据,达到了设计要求。接下来便可以将其转换成VHDL语言在QUARTUS II中进行仿真,生成pof文件下载到FPGA里面。打开Signal Compiler,Family选择Cyclone II,Device选择ALTERA公司的EP2C5T144C6芯片。点击compile,便可以生成工程文件、VHDL代码及配置文件[1]。

以上属于软件仿真,具有速度慢、内容不易控制等缺点。ALTERA的DSP Builder提供的HIL模块可以在Simulink模型与FPGA开发板之间通过JTAG通信口建立联系,从而实现基于MATLAB/DSP Builder平台的硬件仿真。打开HIL模块,设置好工程文件speech.pof路径,连接上FPGA开发板,点击Configure FPGA便可以进行硬件仿真。打开示波器查看仿真结果与软件仿真结果吻合。在QUARTUS II中对生成的工程文件进行编译。整个系统使用了306个LE、214个寄存器、62个管脚,非常节省资源。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)