基于DSP和PCI总线的通信数据采集系统设计

PCI总线是先进的高性能32/64位局部总线。可同时支持多组外围设备,不受制于处理器,数据吞吐量大(32位时峰值高达132Mb/s),并能完全兼容现有的ISA/EISA/MAC等扩展总线。连接到PCI总线上的设备主要分为:主控设备和目标(从)设备两类,接口设计成为PCI总线与设备进行沟通的桥梁。但是PCI总线的规范十分复杂,其接口的实现比ISA等总线要困难得多。目前实现PCI接口的有效方案有两种:使用可编程逻辑器件和使用专门接口芯片。本文中的采集系统就是运用TI公司的TMS320C5410高速定点DSP和PLX公司的PCI9052 PCI总线接口芯片来搭建的。

1 系统功能概述

根据实际应用析需要,系统的主要功能有:

(1)可以同时采集处理一条E1链路上所有32个时际的数据;

(2)对数据进行链路层协议解包后,重新打包茂特定的格式,交给上层系统(PC机)保存或进一步处理。对链路数据状态和采集的统计信息进行监测,定时生成报表,交给上层系统实时显示;

(3)系统应具有尽量大的软件升级功能和灵活性,便于系统提高性能或者应用于其他通信业务数据的采集。

本系统的设计难点主要是如何实现DSP与PCI9052之间高效率的数据通信。在系统中PCI9052通过DSP上专门的高速主机通用接口(host port interface,以下简称HPI口)和DSP进行通信。但是HPI口总线是一个非常特殊的总线,它采用访问寄存器的方式来进行DSP内部数据的读写,HPI口单纯映射到PCI的I/O空间或者存储器空间,有不可避免的缺点。本文提出了一种双映射方法,成功地解决了这一问题,实现了DSP与PCI9052之间方便、高速的数据通信。

2 系统的硬件设计

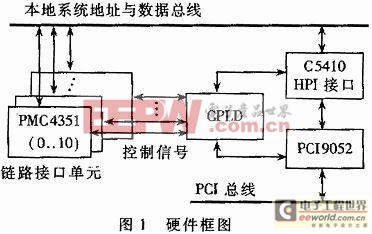

整个硬件系统主要由DSP、PCI总线接口芯片和链路数据采集芯片组成。

本系统采用TI公司的TMS320C5410(以下简称C5410)DSP,该芯片的特点有:

·处理能力可达到100MIPS;

·采用多总线技术,一条指令可以同时访问数据和程序空间,具有高度并行性;

·具有改进型的8位HPI接口,主机通过HPI口可以访问DSP系统的任何一个存储器单元,而且外部访问和DSP内部操作相互独立,互不干扰;

·软件可编程的等待状态发生器,可以灵活地用不同速度的器件组建系统。

数据采集芯片采用了PMC公司的PMC4351.它可以同时采集三个时隙上的数据,可以通过编程选择采集或输出T1、E1数据,支持HDLC协议,可以进行去除CRC标志、复帧标志等预处理,为每小时隙提供128字节的发送FIFO和接收FIFO,有很完善的处理器接口。为了能够同时采集一整条E1链路上的数据,本系统采用了11片PMC4351组成链路数据接口单元。各个芯片之间的接口利用CPLD来完成,它的可编程性为各个组成部分之间的控制和通信提供了相当大的灵活性,也省去了大量外部电路、保证了硬件的方便调试和稳定工作。

具体的硬件框图如图1所示。

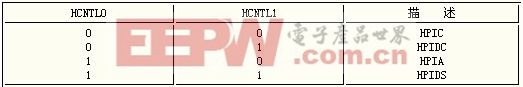

3 DSP的HPI接口与PCI9052的连接

C5410上的增强型8位HPI口为上层系统提供了一个灵活访问DSP内部存储器的并行数据口。上层系统可以通过HPI口自由地读写DSP内部存储器中的任何一个单元。并且C5410为HPI口提供了专门的中断线,这样两个系统可以通过中断进行控制信息交互。HPI为上层系统的访问提供了四个端口,通过这四个端口上层系统可以读写HPI的地址寄存器(HPIA)和控制寄存器(HPIC);通过另外两个端口HPIDC和HPIDS来分别连续和单个读写C5410存储器中的数据。这四个端口由HCNTL0和HCNTL1来寻址,它们的地址分配如表1所示.

表1

本系统采用双映射方式来完成C5410与PCI9052的连接。第一个映射是将HPI口的四个寄存器分别映射到PCI空间的四个16位I/O口上。上层系统可以通过访问I/O端口的方式来访问这四个寄存器,而依照HPI口的工作流程就可以间接地访问C5410内部存储器。这四个寄存器和PCI9052本地I/O空间的对应关系如下:

HPIC--100H

HPIDC--104H

HPIA--108H

HPIDS--10CH

在这种映射方式下,上层系统可通过PCI的I/O访问方式直接访问HPI口的四个寄存器,操作很直观。由于I/O访问无

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)