基于Wishbone总线的UART IP核的设计

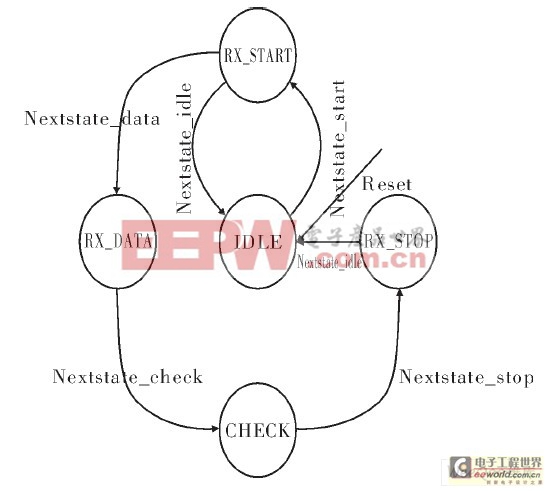

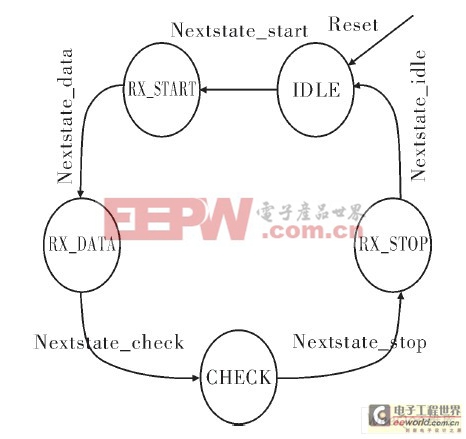

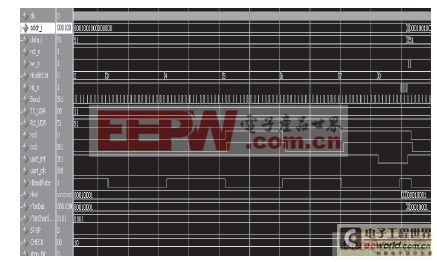

ECK、RX_STOP,它们之间的状态转移,如图3所示。 图3 数据接收模块FSM图 IDLE状态:当产生复位信号或运行至停止状态之后,接收状态机将复位到这种状态。处于IDLE状态时,它等待外部传来的信号从高向低转变,此时视为产生了一个有效的起始位。一旦有效起始位被检测到,有限状态机就会切换到下个状态。 RX_DATA状态:当状态机跳转到此状态时,采样每得到一位数据,就把接收到数据放到准备好的接收移位寄存器中。在设计中需要一个接收计数器来进行计数。当计数器提示数据接收已完成,则状态机会转入下个状态。 CHECK状态:当处于CHECK状态时,通过对实际接收到的数据进行判断得出实际数据的奇偶性,然后再与发送过来的数据的奇偶校验位进行奇偶校验。 如果符合,那么表示接收数据有效,可以传入处理器;如不符,则不传,直接丢弃数据。 RX_STOP状态:无论停止位长度设定为1位或者是2位,有限状态机总是等待1位样本的采样时间,然后抽样停止位。只要一个逻辑采样停止位被检测到,数据接收模块就不会去检查是否停止位的配置出现错误。此时,有限状态机将返回IDLE状态。 2.3 数据发送模块设计 发送模块将从处理器接收到的数据,加上起始位,奇偶检验位和停止位组成规定的格式后串行输出。首先,利用缓存器FIFO存放需要发送的数据,这样处理器可以一次往FIFO中写入多个字节的数据。发送数据时依次从FIFO中每次取出1Byte进行串行输出。 设计采用发送状态机来控制整个模块的发送过程。发送状态机由以下5个状态组成:IDLE、TX_START、TX_DATA、CHECK、TX_STOP,它们的转移关系如图4所示。 图4 数据发送模块FSM图 IDLE状态:在没有接收到将要发送的数据时,发送模块一直处于该状态,此刻一直保持发送模块的数据位为高,当得到主机发出的工作信号时,发生状态跳转,进入下个状态。 TX_START状态:发送模块会先发送一个数据“0”,作为起始位。起始位传送完毕后,转入下个状态。 TX_DATA状态:发送完起始位后,接着发送由主机传来的有效数据。首先把数据存入模块内的移位寄存器中,利用移位寄存器实现并行输入到串行输出的转换。同时计数器开始计数,在发送完8位数据后,计数器清零,FSM随即跳入下个状态。 CHECK状态:当状态机处于这个状态,最后1位数据仍然在传输。传输完成时,状态机将判断校验位。如果校验位无误,则进入下个状态。 TX_STOP状态:在此状态下,根据发送模块的采样结果,将设置相关中断和状态位。发送完毕后,状态机返回IDLE状态。 3 UART IP核的验证方法 对UART IP核的验证主要是在Modelsim软件构建的虚拟平台中进行的,通过编写Testbench(测试代码)作为激励信号,将得到的值与期望值进行比较,从而判断功能是否正确。验证系统框图,如图5所示。 图5 验证系统框图 本次验证施加的测试激励包括两个部分,一部分是模拟发送数据的过程,如总线对于模块内部寄存器的读信号,UART串口输出信号和设备的硬件接口信号等,验证模块的正常功能是否实现;另一部分是模拟接收数据的过程,如外部设备对UART发送的数据接收过程,以及UART 将数据转换发送给微机系统。仿真波形图,如图6所示。 图6 仿真波形图 仿真波形图模拟的是UART在全双工的模式下同时接收一个完整的数据(51,16进制)和发送一个完整的数据(11,16进制)的过程。以接收过程为例:UART首先输出发送UART_INT中断信号,通知处理器准备接收数据,处理器响应中断。UART通过采样脉冲(Baud)将信号写入RX_UDR接收寄存器中,同时接收计数器计数,计数到8时自动清零,中断信号自动清除,随后将接收到的8位数据通过总线模块传入处理器中。发送过程为接收的逆过程。 4 结束语 IP核重用技术以及接口标准化问题是IC设计领域中的研究热点,其应用领域正在不断拓展。本文介绍的基于Wishbone总线的UART IP核的设计方法,通过验证表明了各项功能达到预期要求,为IP核接口的标准化设计提供了依据。此外,该IP核代码全部采用模块化的Verilog-HDL语言编写,便于以后不断完善,具有较强的实际效益。

Wishbone总线 UART IP核 相关文章:

- 基于Verilog HDL的SDX总线与Wishbone总线接口转化的设计与实现(06-05)

- 片上总线Wishbone 学习(九)总线周期之单次写操作(12-15)

- 片上总线Wishbone 学习(八)总线周期之单次读操作(12-15)

- 片上总线Wishbone 学习(六)总线周期之握手协议(12-15)

- 片上总线Wishbone 学习(十二)总线周期之RMW操作(12-15)

- 片上总线Wishbone 学习(五)总线周期之操作发起(12-15)