片上总线Wishbone 学习(六)总线周期之握手协议

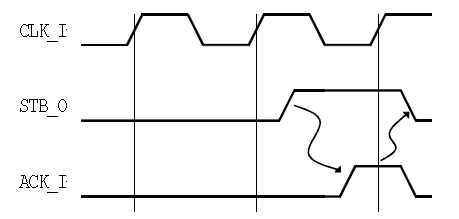

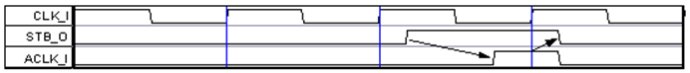

握手发生在主设备和从设备之间。握手协议是主设备和从设备在握手时所遵守的共同规则。如图6,当主设备准备好,它将STB_O信号置高。STB_O信号一直为高,直到从设备通过置高ACK_O、ERR_O、RTY_O对本次操作发起响应。在图7中我们以主设备的ACK_I信号作为示例,后文也如此。通过握手,主设备和从设备不仅可以完成通信,而且可以控制它们之间的通信速率。

图1

如果从设备保证能够在主设备发起操作时及时作出操作成功的响应,其ACK_O信号可以设计为STB_I和CYC_I信号的逻辑与,而ERR_O和RTY_O信号也可以不使用。因此ERR_O和RTY_O信号是可选的,而ACK_O信号是必须的。在点对点连接中,甚至可以将ACK_I信号直接置高。当存在ERR_O和RTY_O信号,主设备当发现ERR_O和RTY_O信号之一有效时如何进行响应取决于主设备的设计。

对于从设备,只有STB_I和CYC_I同时为高时,才能发起对主设备的响应。

实际上,对于主设备,其最小配置为只有ACK_I、CLK_I、CYC_O、RST_I和STB_O;而对于从设备,其最小配置为只有ACK_O、CLK_I、CYC_I、RST_I和STB_I,这里CYC

在图1中,从STB_O到ACK_I存在一个长组合逻辑路径,在实际系统中很可能成为关键路径。因此,在设计中应尽量保证STB_O是触发器的直接输出。如果从STB_O到ACK_I存在一个长组合逻辑路径延迟不能满足设计的时序要求,可将从设备的ACK_O经过触发器寄存后再输出,从而将长组合逻辑打破,但系统的吞吐量也将因此减小。关于如何即打破长组合逻辑又不影响系统的吞吐量,以后的文章将进行详细讨论。

片上总线Wishbone总线周期握手协 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)