片上总线Wishbone 学习(十二)总线周期之RMW操作

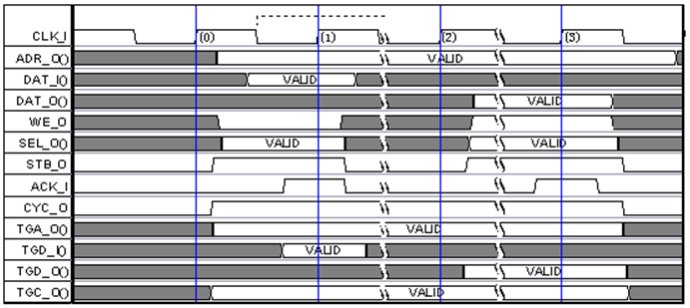

一次RMW操作对于总线来说,本质上是两次子操作,一次读,一次写,只不过这两次子操作必须由同一个主设备的完成,且读数据和写数据的地址相同。"改"是不发生在总线上的,它发生在主设备内部。一个RMW操作的例子如图13所示,其过程如下:

在时钟上升沿0,主设备将地址信号ADR_O()、TGA_O()放到总线上,将WE_O置为低表示读操作,将适当的SEL_O()信号置高通知从设备将数据放在数据总线的适当位置,将CYC_O和TGC_O()置高表示操作正在进行,将STB_O置高表示第一次子操作开始。CYC_O和TGC_O()可以发生在上升沿0以前的任何时刻。

在时钟上升沿1到达之前,从设备检测到主设备发起的操作,将适当的数据放到主设备的DAT_I()和TGD_I(),将主设备的ACK_I置高作为对主设备STB_O的响应。

在时钟上升沿1,主设备发现ACK_I信号为高,将DAT_I()和TGD_I()采样,完成第一次子操作。主设备将STB_O置低表示插入等待。

在时钟上升沿1之后新的上升沿到达之前,从设备检测到主设备将STB_O置低,于是将ACK_I置低。

经过若干等待周期,在上升沿2,主设备将地址信号ADR_O()、TGA_O()放到总线上,将数据信号DAT_O()、TGD_O()放到总线上,将WE_O置为高表示写操作,将适当的SEL_O()信号置高通知从设备将数据总线上哪些信号是有效的,将STB_O置高表示第二次子操作开始。

在时钟上升沿3到达之前,从设备检测到主设备发起的操作,将主设备的ACK_I置高作为对主设备STB_O的响应。

在时钟上升沿3,从设备将DAT_I()和TGD_I()采样;主设备发现ACK_I信号为高,得知第二次子操作完成,于是将STB_O和CYC_O置低表示整个RMW操作完成。

在时钟上升沿之后,从设备发现STB_O为低,于是将ACK_I置低。

图 Wishbone总线的RMW操作

片上总线Wishbone总线周期RMW操 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)