便携式高速数据采集系统设计

针对基于EPP协议的并行端口设备开发的特点与趋势,开发了由A/D转换器AD1671和FIFO存储器ID7202构成的1.25MHz、12Bit的高速数据采集系统,并通过IDT7202与EPP的接口电路实现了采集数据的高速回传。介绍了EPP协议和该采集系统工作原理。

关键词: 增强并行口(EPP) 先进先出存储器(FIFO) A/D转换器AD1671

利用传统的标准并行口(SPP)或RS232进行数据传输,其速度和灵活性受到很大限制。而增强型并行端口EPP(Enhanced Parallel Port)不但与SPP兼容,而且其最高传输速率可达ISA总线的能力(2MHz)。由于便携式计算机日益普及,基于EPP协议开发的便携式微机采集系统将会是一个发展趋势。

通常,低速的数据采集系统可不需要板上的数据缓存区。但当采集速率较高时,数据的回传将占用CPU大量的时间,因而不可能进行其他的控制操作与数值处理,这时就需要足够的缓存区来存放数据。我们在设计高速数据采集系统时采用了FIFO(First In First Out) IDT7202其管脚功能如图1所示。它不但提供了存储空间作为数据的缓冲,而且还在EPP并行总线和A/D转换器之间充当一弹性的存储器,因而无需考虑相互间的同步与协调。FIFO的优点在于读写时序要求简单,内部带有读写的环形指针,在对芯片操作时不需额外的地址信息。随着FIFO芯片存储量的不断增加和价格的不断下降,它将成为传统数据存储器件RAM、SRAM等的有力替代者。方案中的A/D转换器采用了Analog Device 公司的AD1671,最大采集速率可达1.25MHz、12Bit无漏码转换输出。

1 EPP协议简介

EPP协议与标准并行口协议兼容且能完成数据的双向传输,它提供了四种数据传送周期:数据写周期;数据读周期;地址写周期;地址读周期。

在设计中我们把数据周期用于便携机与采集板之间的数据传输,地址周期用于地址的传送与选通。表1列出了DB25插座在EPP协议中的各脚定义。

表1 EPP信号定义

| EPP信号 | 方向 | DB25对应脚 | 描述 |

| nWrite | out | 1 | 低电平写,高电平读 |

| nDataSTB | out | 14 | 低有效,数据读写 |

| nAddrSTB | out | 17 | 低有效,地址读写 |

| AD[8:1] | Bi | 2~9 | 双向数据/地址线 |

| GND | 18~25 | 地线 | |

| nReset | out | 16 | 低有效,外设复位 |

| NINTR | in | 10 | 外设中断,对主机产生 |

| 一个中断请求 | |||

| nWait | in | 11 | 握手信号,低表示可以开始一个 |

| 读写周期,高表示可以 | |||

| 结束一个读写周期 | |||

| Userdfn | in | 12/13/15 | 根据不同外设灵活定义 |

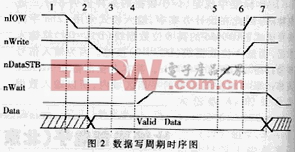

图2是一个数据写周期的例子。

(1) 程序执行一个I/O写周期,写数据到Port4(EPP数据寄存器)。

(2)nWrite变低,数据送到串行口上。

(3)由于nWait为低,表示可以开始一个数据写周期,nDataSTB变低。

(4)等待外设的握手信号(等待nWait变高)。

(5)nDataSTB变高,EPP周期结束。

(6)ISA的I/O周期结束。

(7)nWait变低,表示可以开始下一个数据写周期。

可以看到,整个数据传送过程发生在一个ISA I/O周期内,所以用EPP协议传送数据,系统可以获得接近ISA总线的传输率(500k~2M byte/s)。

2 AD1671控制及采集系统工作原理

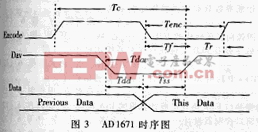

图3是AD1671的AD转换时序图。

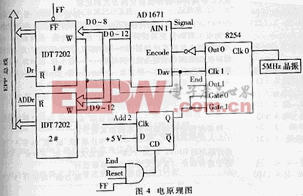

AD1671在Encode信号上升沿开始A/D转换,Dav信号在本次转换完成前一定时间变低,直到Dav出现上升沿表示本次转换结束。为防止数字噪声耦合带来的误差,Encode信号应在Dav信号变低后50ns内变低。系统中通过8254计数器对晶振进行分频来给AD1671提供Encode信号,以满足其工作时序的需要。系统原理图如图4所示。系统初始化时,向8254的Clock0写入计数值,由此可以灵活改变采样间隔,同时写入Clock1的计数值用来控制采样的个数。晶振采用5MHz有源四脚晶振,D触发器实现触发功能,系统工作原理如下:

AD1671在Encode信号上升沿开始A/D转换,Dav信号在本次转换完成前一定时间变低,直到Dav出现上升沿表示本次转换结束。为防止数字噪声耦合带来的误差,Encode信号应在Dav信号变低后50ns内变低。系统中通过8254计数器对晶振进行分频来给AD1671提供Encode信号,以满足其工作时序的需要。系统原理图如图4所示。系统初始化时,向8254的Clock0写入计数值,由此可以灵活改变采样间隔,同时写入Clock1的计数值用来控制采样的个数。晶振采用5MHz有源四脚晶振,D触发器实现触发功能,系统工作原理如下:

系统初始化完成后,经地址译码器产生Add2信号,使D触发器状态翻转,由低变到高,8254计数使能端Gate0、Gate1变高,8254开始方式2的计数。当Clock0的计数时间到时,发出一个宽度为一时钟周期的负脉冲,经反向送入Encode,启动AD1671进行A/D转换。一次转换结束,利用Dav信号将转换的数据写入IDT7202,同时Clock1计数一次。当Clock1计数时间到后,发出一个

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)