基于DSP的CompactFlash卡接口设计

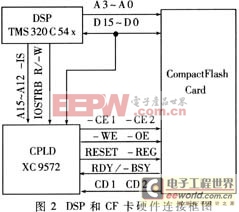

主要由DSP、CF卡和CPLD组成memory连接模式,A3~A0为数据、命令或状态寄存器地址线。D15~D0为数据总线,可16位或8位访问,当片选信号-CE1和-CE2同时有效时,为16位访问格式;当-CE2置高,-CE1单独有效时,为8位访问格式。CD1、CD2为CF卡存在性硬件检测脚,内部和地相连,当CF卡有效插入卡座时,对应卡座上的CD1和CD2拉低,经CPLD逻辑转换可由硬件或软件判断CF卡是否存在。RDY/-BSY为CF卡状态信号,当CF卡忙时,该脚置低,此时DSP不能对其访问及进行其它操作。-WE、-OE为读写有效信号。-REG为寄存器选择信号线,-REG为高时访问数据存储器(命令或数据),为低时访问属性存储器。上电时,CF卡自动完成复位,并在缺省状态下进入memory模式,也可由外部主机经RESET脚对CF卡重新复位。DSP的A15~A12、-IOSTRB、-IS、R/-W脚输出到CPLD,作为I/O空间的读写信号选通和地址译码。

3 软件设计

3.1 CF卡指令及访问格式

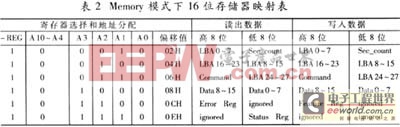

CF卡共有30条命令,在memory模式下16位访问时存储器映射格式如表2所示。

无论以何种方式工作,数据读写的最小单位为一个扇区,8位格式访问时对应一个扇区的数据量为512个字节,16位时对应一个扇区的数据量为256个字。为简化程序设计,DSP用逻辑块地址LBA Lgical Block Addressing 格式访问CF卡数据。LBA地址分段输入,对应的偏移地址分别为02H、04H、06H。CF卡最大存储空间为137Gbyte =228×512 。Sec_count表示一次可访问几个扇区,偏移地址06H高8位 Command 为命令输入。数据从偏移地址08H连续读出或写入一个扇区长度。0CH、0EH空间显示CF卡的状态信息或写入特征命令。

3.2 常用命令编程

CF卡的30条命令在文献 1 中有详细描述,限于篇幅,本文仅介绍CF卡的读写、CF卡信息获取及删除一个扇区命令的编程。另外需注意,尽管CF卡可在Burst方式下达到很高的数据传输速度,但与DSP相比还比较慢,在硬件设计时应确保速度和时序的匹配。

3.2.1 数据读写

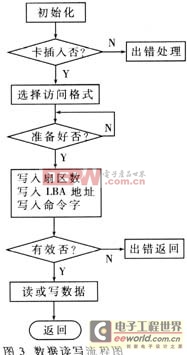

存储器读写流程如图3所示,上电后,可由DSP经RESET脚对CF卡软件复位,等CF卡准备就绪后,写入扇区数、LBA地址、读(20H)或写(30H)命令字。CF卡认可后,连续从扇区缓冲器中读出或写入256个字。注意一点,CF卡要求主机对扇区缓冲器连续读写,否则,在15ms后,CF卡会自动进入睡眠状态,使数据读写出错。

3.2.2 读出CF卡信息

CF卡中有256Byte EPROM专门存放该卡的特征信息,主要包括磁盘柱面数、磁头数、每磁道扇区数、扇区总数、缓冲区大小、缓冲区类型、纠错码位数、公司序列号等,详细内容见参考文献 1 。各公司的CF卡信息内容有一定的差别,以该公司的数据手册为准,命令格式和读写一样,命令字为0ECH,当CF卡收到读信息命令字时,会自动忽略写入扇区数及LBA地址,直接从EPROM中读CF卡信息到扇区缓冲器。

3.2.3 擦除一个扇区

DSP先检查CF卡状态,当CF卡写入有效时,输入指定扇区、LBA地址及擦除命令(0C0H),毋需检查结果状态,该扇区被有效删除后,扇区读出值均为0。

本文介绍的基于DSP的CompactFlash卡接口设计,首先在TMS320c549 EVM 开发板上成功实现了DSP对CF卡的各种常用命令的操作,并通过设置CPLD的逻辑关系,正确实现了对CF卡采用8位或16位格式的操作,多种访问格式提高了应用系统设计的灵活性。本文设计的接口电路具有广泛的应用价值,并已经在数字语音录音系统中获得成功应用。

参考文献

1 CF+and CompactFlash Specification Revision 1.4.

CompactFlash Association, 1999.7

2 TMS320C54x DSP Reference Set Volume 1 CPU and

Peripherals. Texas Instruments Incorporated April 1999

3 TMS320c54x DSP Reference Set Volume 4 Applications

Guide. Texas Instruments Incorporated.October 1996

4 TMS320c54x DSP Reference Set Volume 5 Enhanced

Peripherals.Texas Instruments Incorporated June 1999

5 XC9500 In-System Programmable.CPLD Family.Xilinx lnc.September

15 1999

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)