详细讲解Vivado设计套件带来的益处

是布局布线后的网表。IP 封装器可以创建IP 的IP-XACT 描述,这样用户使用新型IP 集成器就能方便地将IP 集成到未来设计中。IP 封装器在XML 文件中设定了每个IP 的数据。Feist 说一旦IP 封装完成,用IP 集成器功能就可以将IP 集成到设计的其余部分。

Feist 说:“IP 集成器可以让客户在互联层面而非引脚层面将IP 集成到自己的设计中。可以将IP 逐个拖放到自己的设计图(canvas)上,IP 集成器会自动提前检查对应的接口是否兼容。如果兼容,就可以在内核间划一条线,然后集成器会自动编写连接所有引脚的具体RTL。”

Feist 表示:“这里的重点是可以取出已用IP 集成器集成的四五个模块的输出,然后通过封装器再封装。这样就成了一个其他人可以重新使用的IP。这种IP 不一定必须是RTL,可以是布局后的网表,甚至可以是布局布线后的网表模块。这样可以进一步节省集成和验证时间。”

第三大功能是可扩展IP 目录,它使用户能够用他们自己创建的IP 以及赛灵思和第三方厂商许可的IP 创建自己的标准IP 库。赛灵思按照IP-XACT 标准要求创建的该目录能够让设计团队乃至企业更好的组织自己的IP,供整个机构共享使用。Feist 称赛灵思系统生成器(System Generator) 和IP 集成器均已与Vivado 可扩展IP 目录集成,故用户可以轻松访问编目IP 并将其集成到自己的设计项目中。

Vivado 产品营销总监Ramine Roane指出:“以前第三方IP 厂商用Zip 文件交付的IP格式各异,而现在他们交付的IP,不仅格式统一,可立即使用,而且还与Vivado 套件兼容。”

Vivado HLS 把ELS带入主流

可能Vivado 设计套件采用的众多新技术中,最具有前瞻性的要数新的Vivado HLS(高层次综合)技术,这是赛灵思2010 年收购AutoESL 后获得的。在收购这项业界最佳技术之前,赛灵思对商用ESL 解决方案进行了广泛评估。市场调研公司BDTI 的研究结果帮助赛灵思做出了收购决策(见赛灵思中国通讯杂志第36 期“BDTI研究认证以DSP为核心的FPGA设计的高层次综合流程 ”http://china.xilinx.com/china/xcell/xl36/2-7.pdf)。

Feist 表示:“Vivado HLS 全面覆盖C、C++、SystemC,能够进行浮点运算和任意精度浮点运算。这意味着只要用户愿意,可以在算法开发环境而不是典型的硬件开发环境中使用该工具。这样做的优点在于在这个层面开发的算法的验证速度比在RTL 级有数量级的提高。这就是说,既可以让算法提速,又可以探索算法的可行性,并且能够在架构级实现吞吐量、时延和功耗的权衡取舍。”

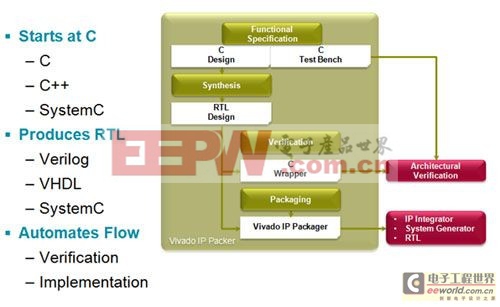

设计人员使用Vivado HLS 工具可以通过各种方式执行各种功能。为了演示方便,Feist 讲解了用户如何通过一个通用的流程进行Vivado HLS 开发IP 并将其集成到自己的设计当中。

在这个流程中,用户先创建一个设计C、C++ 或SystemC 表达式,以及一个用于描述期望的设计行为的C 测试平台。随后用GCC/G++或Visual C++ 仿真器验证设计的系统行为。一旦行为设计运行良好,对应的测试台的问题全部解决,就可以通过Vivado HLS Synthesis 运行设计,生成RTL 设计,代码可以是Verilog,也可以是VHDL。有了RTL 后,随即可以执行设计的Verilog 或VHDL 仿真,或使用工具的C封装器技术创建SystemC 版本。然后可以进行System C架构级仿真,进一步根据之前创建的C 测试平台,验证设计的架构行为和功能。

设计固化后,就可以通过Vivado 设计套件的物理实现流程来运行设计,将设计编程到器件上,在硬件中运行和/或使用IP 封装器将设计转为可重用的IP。随后使用IP 集成器将IP 集成到设计中,或在系统生成器(System Generator) 中运行IP。

图三– Vivado HLS 支持设计团队直接从系统级开始他们的设计.

这只是使用该工具的方法之一。实际上在即将发行的赛灵思Xcell杂志中,安捷伦的Nathan Jachimiec 和赛灵思的Fernando Marinez Vallina 将介绍如何使用Vivado HLS 技术(在ISE设计套件的流程中称为AutoESL 技术)为安捷伦开发UDP 包引擎。

VIVADO 仿真器

除了Vivado HLS,公司还为该套件新开发了一种同时支持Verilog 和VHDL 的混合语言仿真器。Feist 表示,只需要单击鼠标,用户就可以启动行为仿真,然后从集成波形查看器中查看结果。通过采用最新性能优化的仿真内核,可加速行为级仿真速度,执行速度比赛灵思ISE 设计套件仿真器快三倍。采用硬件协仿真,门级仿真速度则可加快100 倍。

2012供货情况

之前赛灵思ISE 设计套件针对不同类型设计者(逻辑,嵌入式,DSP和系统)所发行的四个版本,赛灵思将推出Vivado 设计套件的两个版本。其中,Vivado 基础设计版本包括新型IP 工具和V

FPGA IP 嵌入式 PLD CPLD SoC 数字信号处理 消费电子 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)