满足28 nm迫切的低功耗需求

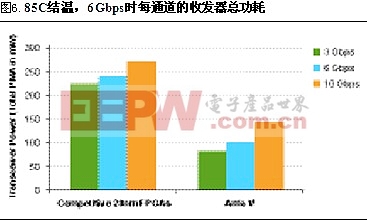

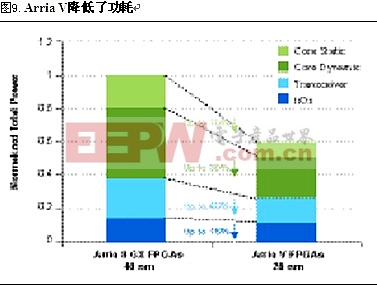

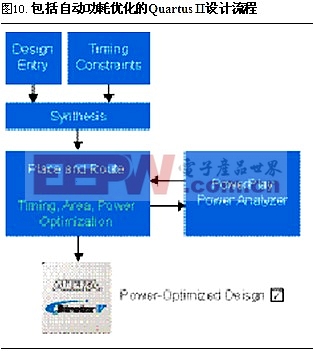

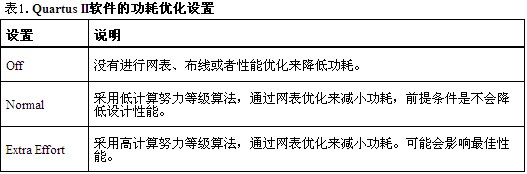

移动电视、GPS导航,以及传统的电话和文本服务等。主动应用功耗现在是电池使用时间的主要因素。SiON逻辑门技术由于具有较小的栅极电容,因此,动态功耗比HKMG (高K金属门)低,对于功耗受限的应用,提供的解决方案具有较低的总功耗,成本和风险也很低。” 28LP工艺具有较低的栅极电容,有源栅极电容比28HPL低30%。在Cyclone V和Arria V器件中,Altera还采用了其他方法来降低器件电容,包括用于存储器控制器的硬核IP、PCI Express,还提供收发器协议支持,减小了管芯面积及其相关电容。最后,与Stratix V器件相比,Altera还针对Cyclone V和Arria V器件的基本体系结构模块进行了优化。这些优化措施减小了硅片面积以及相关的电容,使得28LP器件系列满足了目标应用的性能要求。例如,Arria V器件逻辑阵列模块(LAB,10个自适应逻辑模块)的管芯面积比Stratix V LAB小40%。Cyclone V和Arria V器件的硬核存储器控制器也同样减小了管芯面积以及外部存储器接口的相关电容。所有减小器件电容的这些措施都降低了动态功耗,符合下面熟悉的功耗公式,其中,C表示开关电路的电容: 动态功耗 = 1/2CV 2 × f Altera还降低了器件收发器的动态功耗。Altera丰富的收发器设计专业知识在业界是首屈一指的,其独特的优势反映在收发器较低的动态功耗上。例如,在6 Gbps,Arria V收发器功耗不到100mW,比28-nm竞争FPGA的功耗低得多,如85C结温,6 Gbps时每通道的收发器总功耗所示。对于采用了36个收发器Arria V器件的设计,功耗降低了5W多。 Altera在28-nm节点实现了较低的收发器功耗,这是因为我们经过了多年的磨炼,增强了专用体系结构。在可编程逻辑业界,只有我们能够持续不断的发展高级收发器技术,因此,功耗一直在逐步降低。竞争解决方案每一代产品的收发器功耗都在增加,如所示,画出了收发器物理介质附加层(PMA)功耗与多代FPGA之间的关系曲线。 通过这些静态和动态功耗优化措施,Altera基于28LP的FPGA总功耗比前几代器件降低了40%,全面降低了功耗,如Cyclone V降低了功耗所示。 显示了Arria V器件相似的结果。 通过软件创新降低功耗 在工艺和体系结构创新基础上,Altera在Quartus II的软件功耗优化方面进行了大量的投入。功耗驱动的编译使用功耗驱动综合和功耗驱动布局布线功能,主要用于降低设计的总功耗。对于设计人员而言,这种功耗驱动的方法是透明的,通过简单编译设置来实现。设计工程师将时序约束简单地设置为设计输入过程的一部分,对设计进行综合,满足性能要求。Quartus II为每一功能模块自动选择所需的性能,并通过功耗预知布局布线和时钟技术来降低功耗,如包括自动功耗优化的Quartus II设计流程所示。 Quartus II软件在不同的编译阶段采取各种措施来降低设计的总功耗。在综合阶段,Quartus II软件提取时钟使能信号,进行时钟选通,减少对RAM模块的访问,重新构建逻辑以避免高触发网。在适配阶段,Quartus II软件找到高触发网,以降低动态功耗,优化逻辑布局,减小时钟功耗,实现高功效DSP和RAM模块配置。最后,在汇编级,Quartus II软件对未使用的电路进行编程,尽可能减小触发,或者进行关断。最终的设计以最低的功耗满足了设计人员的时序要求。 如Quartus II软件的功耗优化设置所示,设计人员可以选择不同级别的功耗优化选项,以满足设计约束要求。选择Extra Effort设置,最大限度的降低功耗,代价是较长的编译时间。不同的设计,选择不同的努力等级会有不同的结果。这一特性降低了功耗,不需要设计人员的干预,同时减小了对设计性能的影响。此外,在详细的电路模型和高级统计方法的指导下进行功耗优化,估算哪些信号是被经常触发的。通过这些信息,Altera确定高功效实现方法,不需要设计人员的额外输入(例如,对设计进行耗时的仿真以确定开关速率)。 基准测试 Altera为业界提供最先进、功耗最低的FPGA。通过基准测试来估算各类典型应用的总功耗,进一步表明了Arria V器件相对于竞争28-nm器件的低功耗优势。Arria V FPGA和竞争28-nm FPGA的总功耗对此显示了这些基准测试的结果,这些都记录在Altera wiki网站上,以便进一步进行研究学习。 结论 Altera低功耗28-nm器件的优点包括,降低产品成本,降低或者放宽功耗预算,较低的散热要求,能够满足更多的市场需求,在同样的散热和功耗预算内进一步提高性能等。采用最全面的方法降低28-nm产品的功耗,Altera帮助设计人员满足了迫切的低功耗需求。

- ALTERA FPGA在微处理器系统中的在应用配置(07-09)

- 藏在系统核心芯片中的DRAM控制器(12-10)

- 真实环境中的系统设计(09-09)

- IoT促进了低功耗的发展(12-05)

- 闪存革命无处不在(12-25)

- 悬崖边上的CPU设计师: 现在该往哪里去?(11-10)