采用低功耗28-nm FPGA降低系统总成本

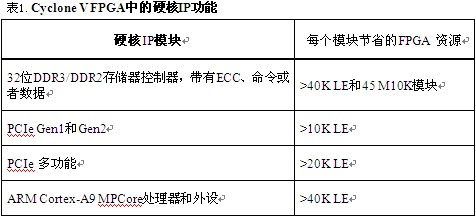

硬核实现所节省的资源量。

成熟可靠的收发器,针对各种数据速率进行了优化,缩短了调试时间

Altera的28-nm系列产品引入了模块化收发器,支持设计人员满足实际应用的器件性能需求。在Altera所有28-nms FPGA系列中,这种收发器使用了相同的基本体系结构,最大工作速率从3.125-Gbps直至28-Gbps。正如Stratix V和Arria V器件一样,Cyclone V收发器能够在几种不同的速率设置之间动态切换,可以降速来降低功耗。这种选择功能为降低系统平均功耗提供了一种方法,在空闲时,收发器工作在最小速率,根据需要切换到高速工作。

如果I/O扩展等应用只需要5-Gbps或者速率更低的收发器,那么,不会出现28-Gbps工作时大型晶体管那样的功耗和成本。相反,收发器以最低功耗和最低成本实现了3.125-Gbps和5-Gbps性能,Cyclone V FPGA系列能够很好的适应设计。与Stratix V和Arria V器件中的收发器相似,Cyclone V FPGA收发器支持多种协议,包括,3G SDI、千兆以太网(GbE)、CPRI、Display Port、PCIe、Serial ATA (SATA)和Serial RapidIO®等。Altera收发器信号完整性以及通过收发器工具包实现的实时调试功能,能够节省数星期的电路板开发和调试时间。

f 关于收发器工具包的详细信息,请参考Altera网站的收发器工具包页面。

仅采用两种电压轨,简化了电源分配,降低了成本

在所有低成本FPGA中,Cyclone V FPGA需要的电压轨数量最少。它们有内置片内电压稳压器,因此,您只需要使用两种电压轨来同时支持逻辑和收发器电源。这样,可以不需要板上电压稳压器,避免了布线拥塞,减少了所需的电路板层数,从而简化了电路板设计。竞争器件至少需要三种电压轨来支持内核、I/O和收发器逻辑。额外的电源轨需要增加元件以及PCB面积,还可能会带来布线拥塞问题,因此,在您的电路板开发预算中,成本可能会增加10到30美元。

fPLL可合成任意频率,不需要额外的振荡器

Altera 28-nm器件的通用锁相环是fPLL,它具有高级分段式频率合成以及M/N频率实现功能。在标准PLL中,M和N值都是整数。Altera采用了delta-sigma调制器,并在反馈通路中使用了32位M和N值,支持反馈M分频器采用分段值。这支持实现精确的频率合成功能。能够合成任意时钟频率,fPLL可以替代电路板上的振荡器,从而降低了电路板成本,减小了电路板面积。

智能引脚布局提高了可布线能力,缩短了调试时间

Cyclone V FPGA以最低的开发成本提供最好的信号完整性。采用了常规棋盘式电源和地模式,简化了布板。此外,器件左侧是常规的收发器布局,并进行重复,而接收器总是在外部,从而实现了最佳信号完整性。还尽量远离收发器放置存储器I/O引脚,相对于收发器进行屏蔽。Altera的方法是,首先通过避免引脚布局问题,减少在耗时的调试过程上的投入。

Altera系统设计工具降低了总体拥有成本

Altera的集成设计环境,包括Quartus II软件,为FPGA业界提供最先进的工具集,降低了开发成本,缩短了产品面市时间。采用Quartus II软件,从概念构思到产品,您能够迅速高效的设计整个FPGA。它提供类似ASIC的时序收敛工具(TimeQuest时序分析器),支持很多在系统调试功能。其高效能特性包括,Qsys系统集成工具、系统控制器、收发器工具包,以及DSP Builder和SoC虚拟目标软件平台。

采用Qsys实现系统集成

Qsys是下一代SOPC Builder工具,用于帮助设计人员构建并调整系统。Qsys支持用户开发的以及商用IP模块的快速集成,加速了您的设计流程,提高了效能。而且,Qsys支持分层设计,简化了大规模设计的管理,例如,很容易实现并测试具有数百个元件的系统,并且可以管理,方便进行设计重用。基于芯片网络体系结构,以及自动流水线,其按键式性能互联比SOPC Builder提高了2倍。最终,Qsys帮助设计人员缩短了数月的开发时间,在几天而不是几星期内实现PCIe等内核。

通过系统控制台进行系统研究和调试

利用系统控制台这一工具,用户可以使用系统级会话功能,通过方便简单的软件应用编程接口(API),在命令行或者系统控制台图形用户界面(GUI)中,采用脚本,或者交互式运行,在更高的抽象级上实时调试FPGA。系统控制台非常适合电路板开发等任务,使设计人员能够通过JTAG或者TCP/IP来使用和控制FPGA硬件,从而节省了数星期的时间。

采用具有高级模块库的DSP Builder进行DSP应用设计

利用DSP Builder,您可以采用世界上最知名的DSP设计工具MATLAB® Simulink®来设计FPGA。采用这一设计工具,您能够继续停留在自己熟悉的EDA环境中,使用易于理解的原理图输入工具进行

- ALTERA FPGA在微处理器系统中的在应用配置(07-09)

- 藏在系统核心芯片中的DRAM控制器(12-10)

- 真实环境中的系统设计(09-09)

- IoT促进了低功耗的发展(12-05)

- 闪存革命无处不在(12-25)

- 悬崖边上的CPU设计师: 现在该往哪里去?(11-10)