多核DSP系统高速传输核心的IP设计

时间:04-22

来源:互联网

点击:

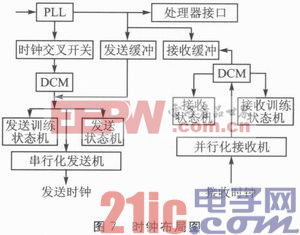

发送时钟模块的主要功能包括:

①使用DCM的相移功能,提供RapidIO发送数据合适的采样时钟相位,包括从发送缓冲区将数据提取出来,以及在发送数据前提供的较好的冗余时钟相位,保证时钟能正确地采集发送的数据和帧同步信号。

②在进行数据串行化的时候,通过DCM的倍频功能将上层模块的数据发送变成双数据进行发送,即时钟的上沿和下沿同时发送数据。

③通过差分引脚将LVTTL发送时钟变为LVDS差分时钟进行发送。

接收时钟模块中的主要功能包括:

①接收到的差分LVDS时钟转换为LVTTL时钟。

②对接收到的时钟信号通过DCM对其进行分频,以便能够正确地将接收到的DDR数据转化为SDR数据。

③对接收到的时钟通过DCM进行相位移动,以便为接收缓冲区正确地接收数据提供正确的采样时钟相位。

除了此处提到的模块,RapidIO协议专用集成电路内部还有串行和并行模块,接口模块等,在此就不一一介绍了。

结语

适用于多核DSP系统的高速互联接口对于研究多核的体系结构具有实际意义。研制满足RapidIO协议的专用集成电路不仅可以快速实现网络结构,而且可以降低系统的功耗,提高可靠性,具有很好的应用价值。

- 基于FPGA实现DSP与RapidIO网络互联(04-24)

- 应用FPGA实现DSP与RapidIO网络互联(02-22)

- 串行RapidIO连接功能增强DSP协处理能力(04-30)

- 在基带处理中使用串行RapidIO协议进行DSP互连(07-23)

- CPS1432交换芯片的串行RapidIO互连技术(09-12)

- 串行RapidIO交换技术(10-23)