多核DSP系统高速传输核心的IP设计

行负载均衡,从而实现更高的运算效率。

3 RapidIO专用电路中核心IP模块设计

RapidIO协议可以用大规模集成电路来实现,通过协议本身的控制作用完成对数据通路的控制作用。因此RapidIO专用集成电路就是基于这个协议的框架结构,从根本上解决嵌入式系统互连的通信问题,从而提高系统的整体性能。

3.1 发送和接收IP模块设计

发送和接收模块主要围绕采用的双端口存储器进行复杂的控制逻辑设计。根据协议的要求,可在RapidIO专用电路的双口SRAM中规定一个口写数据,一个口读数据,从而降低控制逻辑设计的复杂性。在本设计中规定A口是只写的,而B口是只读的,它们的数据宽度为32位,深度为1024。

3.1.1 发送缓冲IP模块设计

在双口SRAM的外围设计了较复杂的控制逻辑构成发送缓冲区,A口和B口的地址计数器的地址由两部分组成:ID号和地址递加计数逻辑。A口的输入数据来自于RapidIO封装的数据帧,而B口的输出数据又被送到了RapidIO发送状态机内,只不过B口的数据是需要重发的数据。

因为RapidIO数据帧最大为68个双字,发送窗口数被设计成7,所以已经发送的数据在这个双口SRAM中是分段保存的。当RapidIO发送状态机开始发送数据,同时对数据进行封装时,A口的写信号有效,并且A口的计数器进行递增计数,递增计数器和段地址构成了A口的有效地址。这样已发送的数据就被保存在这个以双口SRAM为核的缓冲区队列中(最多为476个双字数据)。在这个双口SRAM的外围设计了段指示变量用来指示在该段中保存字数据的个数(因为发送的数据可能有不够256个字节,即64个双字的情况)。

相邻节点返回的数据响应帧内,包含相邻节点希望接收的下一个数据帧的序号ID,当数据响应帧类型为datanot accept或data retry类型时,激活了发送状态机内的重发机制,B口当前地址和A口的段指示变量进行比较,当B口的当前地址和A口相应的段指示变量相等时,通知发送状态机该数据已经被重新发送完毕,结束帧的发送。只有该帧数据的正确的响应帧被接收到时,A口才能继续发送新的数据,并且发送缓冲区的窗口向前滑动。通过使用这种方法,已发送的数据就源源不断地保存在这个缓冲区队列中,而且不会丢失。

3.1.2 接收缓冲IP模块设计

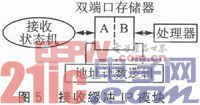

在双口SRAM的周围加入了一些外围的控制电路构成了接收缓冲区。双口SRAM的A口和接收状态机相连,双口SRAM的B口和处理器接口相连。A口和B口分别使用了地址计数逻辑。接收缓冲IP模块如图5所示。

由于RapidIO的一个数据帧是以272字节封装的,并且在数据帧的第80个字节处插入了一个CRC校验序列,这样就增加了判断的难度。当接收机开始接收数据帧内嵌入的第一个CRC校验序列时,通过接收状态机进行判断:当接收到的第一个CRC校验序列和接收状态机本地产生的CRC一样时,A口的地址计数电路继续计数;当接收到的第一个CRC校验序列和接收状态机本地产生的CRC不一样时,说明前面接收到的数据是无效的,此时地址计数电路停止计数,并且地址指示变量减去20。

当接收完一个数据帧内的所有有效数据时(不包括数据帧末尾的CRC校验码),地址计数电路停止计数,同时在接收状态机内进行判断:当接收到的数据帧末尾的CRC校验序列和接收状态机本地产生的CRC校验序列一致时,地址指示变量的值不变;当接收到的数据帧末尾的CRC校验序列和接收状态机本地产生的CRC校验序列不一致时,地址指示变量减63(标准的数据帧内的有效数据是64个字)。通过这样的方法在由这个双口SRAM构造的接收数据缓冲区内保存了一个完整有效的数据帧。

3.2 发送/接收状态机

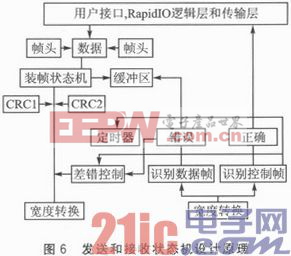

发送状态机和接收状态机模块包含了RapidIO协议的差错控制和流量控制的功能。差错控制功能主要是通过使用CRC校验机制和定时器机制来完成的。发送状态机和接收状态机是通过相互交换内部信息来实现对数据进行差错控制和流量控制的,如图6所示。

3.2.1 发送状态机模块设计

如图6所示,来自处理器接口的原始数据依次传送到RapidIO的逻辑层和物理层时,在数据的头部封装了地址、序号和长度等头部信息,同时发送状态机得到每个数据的CRC码;当数据大于80个字节时,在第80个字节的后面插入1个CRC码,然后在该数据帧的尾部插入1个CRC码,这样就将一个原始的数据转换成了1个RapidIO数据帧,然后将这个封装的数据帧传到串行化数据模块进行发送。

如果数据帧被对方节点正确的接收,则发送端口可以继续发送数据;如果数据帧被对方拒绝接收,则停止数据的继续发送,并且接收端口和发送端口通过同步控制帧重新进行端口同步,当这种同步重新建立后发送端口才可以继续发送数据;在发送状态机模块中采用了滑动窗口技术,一方面可大大提高数据的吞吐量;另一方面可以尽量避免由于接收方缓冲区资源不足而导致的多次发送失败。

3.2.2 接收状态机模块设计

当接收到数据帧后,对接收到的数据帧通过CRC校验机制进行错误检查,同时得到帧的序号和设备号等信息,并且将数据帧的接收状态通知本地发送端口,由本地发送端口根据接收数据的状态作出判断,然后向对方节点设备发送响应帧信号。

当接收状态机接收到一个完整的消息后,则由接收状态机向本地处理器接口发出中断信号,通知处理器将接收缓冲区内的数据取出;当接收状态机接收到控制帧后,根据控制帧的类型作出判断,如果是错误数据的响应帧,则本地发送端口和接收端口同时处于停止发送和接收数据状态,并且通知本地发送端口发送link请求帧和link相应帧,使得接收和发送链路重新建立连接;如果是用于链路控制的控制帧,则本地发送端口根据接收到的控制帧类型向相邻节点发送相应的响应控制帧。

3.3 时钟信号设计

RapidIO协议规定使用双数据时钟发送和接收数据。

在专用电路内的时钟布局分为发送时钟模块和接收时钟模块两大子模块。对时钟的分频和倍频是通过专用集成电路内的数字时钟管理器DCM完成的。来自处理器的输出时钟要驱动专用电路芯片和其他外设,所以在专用电路的内部加入PLL,保证输出时钟能提供足够的时钟频率、驱动能力和较陡的时钟边沿。时钟资源在专用电路内的布局如图7所示。

- 基于FPGA实现DSP与RapidIO网络互联(04-24)

- 应用FPGA实现DSP与RapidIO网络互联(02-22)

- 串行RapidIO连接功能增强DSP协处理能力(04-30)

- 在基带处理中使用串行RapidIO协议进行DSP互连(07-23)

- CPS1432交换芯片的串行RapidIO互连技术(09-12)

- 串行RapidIO交换技术(10-23)