CPS1432交换芯片的串行RapidIO互连技术

引言

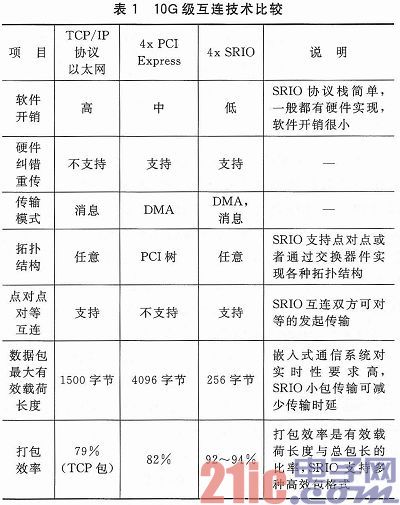

串行RapidIO(SRIO)是针对嵌入式系统内部高速互连应用而设计的,数据打包效率高、传输时延小、协议及流控机制简单、纠错重传机制和协议栈易于用硬件实现,降低了软件复杂度,支持多种物理层技术和传输模式,易于扩展。SRIO引脚少、成本低,便于器件之间的互连。表1列出10G级互连技术的比较。

通过比较可以看出,SRIO可以满足高性能嵌入式系统芯片间及板间互连对带宽、成本、灵活性和可靠性越来越高的要求。本文介绍基于SRIO交换芯片CPS1432的高速处理系统,从总体设计、硬件设计和软件设计3个方面介绍RapidIO互连技术方案。

1 系统设计

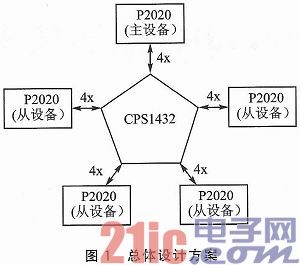

RapidIO网络主要由终端器件(End Point)和交换器件(Switch)组成。在本方案中终端器件采用P2020型CPU,运行嵌入式Linux系统,交换器件采用CPS1432,两者组成星型拓扑结构。总体设计方案如图1所示。

SRIO物理层支持全双丁传输和1x、2x及4x三种连接方式,采用8/10 b编码,为了提高系统的吞吐量,本方案采用4x方式连接,理论带宽可达到10 Gbps。整个系统的终端器件中有且只有一个ID为0的主设备,其他终端器件都是从设备。在系统初始化过程中,主设备对各个从设备进行枚举,并为从设备分配一个非0的ID,这些ID类似于以太网中的MAC地址。在枚举过程中,通过发送维护包,对交换器件CPS1432的各个端口进行设置,建立各个端口与终端器件的对应关系,初始化交换芯片各个端口的路由表。当整个系统枚举完成后,终端器件发送包含目的ID的数据包,即可通过CPS1432转发到目的终端器件的对应端口,从而实现互连互通。

2 硬件方案设计

2. 1 硬件设计

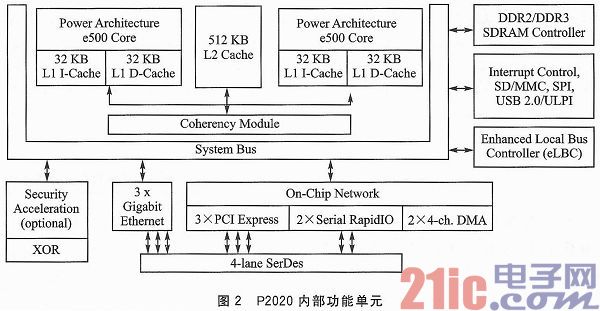

P2020是飞思卡尔公司的高性能双核通信处理器,基于45 nm工艺,采用e500 Power Architecture核心,主频可达1.2 GHz,对应的单核器件为P2010。两者均集成了丰富的接口,包括SerDes、千兆以太网、PCI—Express、RapidIO以及USB等。内部4个SerDes通道可在2个SRIO端口、3个PCI-Express端口以及2个SGMII端口之间进行分配,P2020内部功能单元如图2所示。

P2020内部集成了符合RapidIO Interconnect Specification1.2版本规范的RapidIO控制器,控制器由RapidIO端口和RapidIO消息单元(RMU)组成。P2020的2个SRIO端口都支持1x或4x的物理链路,单条SerDes链路最大支持3.125 Gbps的波特率,4x端口理论峰值带宽为10 Gbps。消息传递单元支持2个数据消息发送控制器(outbound nlessage contro ller)、2个数据消息接收控制器(inbound message controller)、1个门铃消息发送控制器(outbound doorbell controller)、1个门铃消息接收控制器(inbound doorbell cont roller)以及1个端口写接收控制器(inbound port—write controller)。消息传递单元支持3种操作模式:直接模式(Direct model)、队列模式(Chainingmodel)和多播模式(Mul ticast model)。支持硬件的错误检查和重发机制,减轻了CPU的负担。

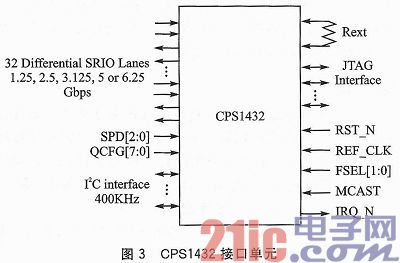

CPS1432是IDT公司的RapidIO交换芯片,基于RapidIO 2.1规范(向下兼容),共有32路串行通道,可以灵活配置为8个4x,14个2x,14个1x的端口工作方式,端口速率最大支持到6.25 Gbps,芯片内部交换带宽达到160 Gbps,广泛地应用于板内及板间芯片的RapidIO互连。该芯片支持上电配置引脚来进行配置,也可以通过SRIO、I2C总线或JTAG接口直接操作内部寄存器,同时I2C总线接口支持主模式,可从外部I2C EPROM中直接读取配置数据,其接口单元如图3所示。

为了便于配置不同的模式,本系统将P2020和CPS1432的配置引脚都引入了FPGA,CPS1432的I2C总线接口连接到板载CPU的I2C总线接口上,由CPU进行内部寄存器的读写控制。上电复位时,通过P2020的配置引脚cfg_IO_ports[0:3]将4个SerDes通道配置为一个4x的SRIO端口,速率3.125 Gbps,根据芯片要求,Serdes参考时钟应选择125 MHz。通过CP S1432的配置引脚QCFG[7:0]和SPD[2:0]将32路串行链路配置为8个4x的SRIO端口,速率均为3.125 Gbps。

2.2 注意事项

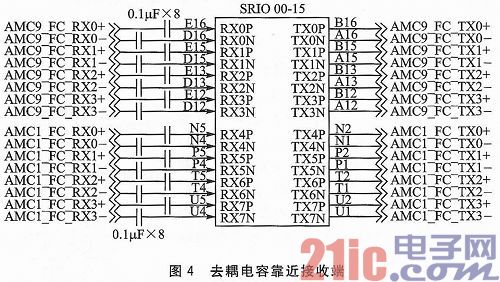

在电路设计上,由于SRIO引脚数量少,互连相对简单。收发信号之间采用交流耦合方式,在数据接收端串接0.1μF的去耦电容,如图4所示。电容推荐采用0402封装,布局上靠近芯片接收端引脚放置,且4个通道的耦合电容与芯片引脚之间的走线等长。

在PCB设计方面,基于信号完整性的考虑,需注意以下几点:

①对于常用的FR4板材,要注意叠层和走线的线宽,满足差分阻抗100Ω;

②差分线对内要求严格等长,由于SRIO收发信号独立,对于2x或4x的链路,收发各自的差分对之间也要做等长处理(本系统要求相差10 mil以内);

③尽量全直线走线,

- 串行RapidIO连接功能增强DSP协处理能力(04-30)

- 采用串行RapidIO连接功能增强DSP协处理能力(10-09)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)