一种适用于高速接口电路的新型均衡电路

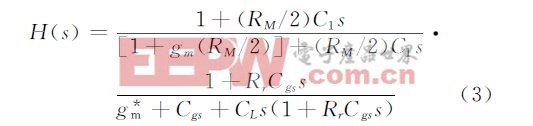

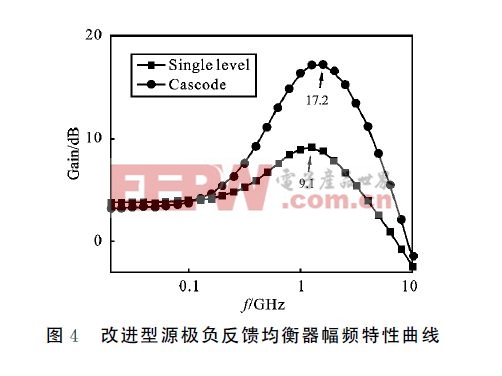

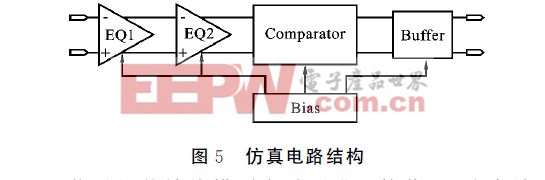

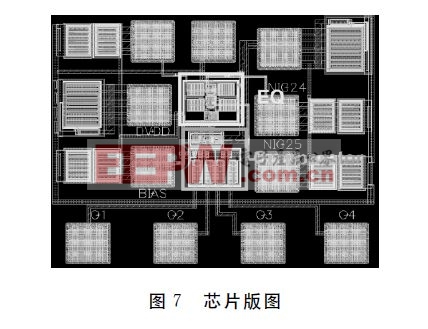

M11的1/10.采用这种有源电感的结构避免了使用片上电感,对芯片成本的降低起到关键性作用.对于公式(1),改进型源极负反馈均衡器的传输函数为: 即将式(1)中负载引入的极点修改为有源电感负载网络,其中Rr代表有源电感等效电阻,Cgs为式(2)中M2栅极电容,g*m为M2跨导.引入系统传输函数的零点为-1/RrCgs ,调节该零点位置,补偿和优化电路均衡效果。 5 仿真验证及版图电路使用两级均衡器提高均衡效果,后级采用交叉耦合差分接收器提高整个系统增益.如图4所示,两级级联后均衡器高频补偿增益达到17.2dB。 全芯片电路结构如图5所示.电路使用两级均衡器提高均衡效果,输入信号为高速差分信号,经传输线模型衰减后进入均衡器,后级输入限幅比较器将差分信号转换为单端信号.仿真采用Hspice,信号速率5Gbit/s,共模电平1.25V,差分信号摆幅600mV,上升下降延时各50ps。 信号经传输线模型衰减后进入接收器,仿真结果如图6所示.图6(a)为经传输线衰减后信号,(b)为经过两级均衡器后输出信号,(c)为均衡器输出经限幅放大器后输出信号.从波形可以看出该电路在信号频率达到5Gbit/s时仍能很好还原数据波形,并观察到明显的均衡效果.其他仿真数据见表1。 该电路最后使用0.13μm CMOS工艺实现,芯片面积约为0.26mm2,电路包括两级级联的均衡器,交叉耦合接比较器作为限幅放大器及后级驱动电路,后仿芯片功耗为34.7mW,芯片版图概貌如图7所示。 6 结束语 文中使用0.13μm CMOS实现了一款可以补偿高频信号传输线损耗的新型均衡器结构.仿真结果验证得到,该电路可以接收速率高达5Gbit/s数据信号,并对传输线损耗造成的高频衰减提供了有效的补偿.在设计中,使用了对称负载和有源电感等技术,避免了使用片上电感.对电路的噪声抑制和均衡效果起到了明显的促进.电路仿真使用Hspice,功耗仿真结果满足设计需求

- Thunderbolt超高速接口技术解析(06-05)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)