基于CPCI总线的FPGA加载设计

0 引言

由于具有极强的实时性和并行处理能力,FPGA芯片在无线通信、信号处理等领域得到了广泛应用。

作为一种半定制电路,FPGA 的使用非常灵活,对于同一片FPGA,通过加载不同的编程数据可以产生不同的电路功能。但是,由于基于静态只读存储器(SRAM,Static Random Access Memory)的架构,FPGA 掉电后就变为白片,再次上电时需要EPROM 芯片对其进行加载。对于需要切换算法的场景,就需要通过上位机对其进行动态加载。本文在深入分析了FPGA 配置流程和理解CPCI 总线的基础上,设计实现了基于CPCI 总线的FPGA 动态加载。

1 硬件设计

系统中需要对三片Virtex5 系列的芯片进行动态加载,整个硬件结构框图如图1 所示。Spartan-3E与PCI9656直接相连,作为主控制芯片Spartan-3E一方面接收来自CPCI 总线的数据,对V5 芯片进行参数下载、动态加载等;另一方面接收V5 芯片的传递来的各类数据,根据上层软件的请求,将各类状态信息或实时处理数据上传到工控机。

2 PCI9656 芯片介绍

PCI 接口协议比较复杂,接口电路实现起来较为困难,在设计基于PCI或CPCI总线的数字设备时,采用各公司提供的通用PCI I/O 芯片或IP 核,可简化复杂的PCI 接口设计。PCI9656 是PLX 公司为高速PCI 总线应用而设计的通用I/O 芯片,PCI9656配备DMA 引擎、可编程直接主控和直接从属数据传输模式以及PCI 信息传输功能。零等待状态突发操作,PCI 总线突发传输速度高达528 MB/s,局域总线突发传输速度高达264 MB/s.

PCI9656 的局部总线有M、C、J 三种接口模式,为了简化数据传输控制逻辑,设计中采用了C 模式,该接口模式为适合大多数处理器的通用模式。在数据传输中,PCI9656 传输数据有两种模式:突发模式和直接内存存取(DMA,Direct Memory Access)模式。其中突发模式一般用于传递少量不连续数据的场合,DMA模式则用于传递大量连续数据的场合。

在设计中,所有的参数上传、下载都是通过突发模式传输的,而三片V5 芯片的加载,连续处理数据的上传则是通过DMA 模式完成的。

3 FPGA 加载概述

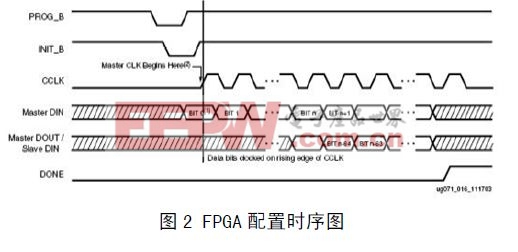

FPGA 的加载有多种模式,主要有主串模式(Master Serial),从串模式(Slave Serial),边界扫描模式(Boundary Scan),SPI 模式和SelectMap 模式等。设计中采用了Slave Serial 模式,该模式由外部处理器或控制器提供时钟,总共用到了CCLK,PROG_B,DONE,INIT_B,DIN 5 个管脚,其中CCLK 管脚为加载提供时钟,当PROG_B 信号置低300ns后检查INIT_B信号为高电平即可通过DIN管脚送入数据进行加载,当数据加载完成后检查DONE管脚为高电平表示配置完成。Slave Serial 模式的时序图如图2 所示。

FPGA 的配置文件有多种不同的格式,例如BIT,BRT,BIN,MCS,EXO,TEK,HEX 等。由于ISE 软件调用Bit Gen 程序直接生成的文件格式为BIT,故系统如能直接用BIT 文件作为配置文件将省去文件转换的麻烦,通过分析发现BIT 文件与BIN(直接二进制配置文件)文件相比仅仅多了文件头,又由于FPGA 配置过程中会进行同步、器件ID 检查等操作,因此多出的文件头部分会自动忽略,故而通过Slave Serial 方式直接下载BIT 文件配置FPGA 是可行的。

4 硬件模块设计

Spartan-3E中的程序设计包含PCI9656配置模块,负责对PCI9656 芯片进行初始化;PCI9656 接口模块,负责与PCI9656 进行数据交互;参数模块,负责将接收的参数重新分配给三个芯片或者将一些状态信息上传到工控机;FPGA 配置模块负责将接收到的FPGA 的BIT 文件流通过FIFO 将不连续数据缓冲为连续数据,并触发配置逻辑,对FPGA 进行配置。

系统的模块划分如图3所示。

4.1 PCI9656 配置模块

PCI9656 一般都有对应的EEPROM,用于上电时初始化芯片工作的相关参数。根据实际需求,由于需要初始化的参数较少,PCB 设计中没有放置EEPROM,需要Spartan-3 E 通过本地总线对其进行初始化。对于PCI9656,初始化其PCI Subsystem ID、PCI Subsystem、Vendor ID 后,在工控机就可以进行其他配置,配置这两个参数只需要通过本地总线往地址0X2C写入相应数据即可。

4.2 参数模块

由于以突发模式下载到Spartan-3E 的数据是以32 bit 为单位的,且三片FPGA 需要的参数各不相同,因此需要对下载到Spartan-3E 的数据进行整理分类,再根据不同需求,下载到三片FPGA 中去。

状态参数的上传与下载流程相反。

4.3 FPGA 加载模块

DMA 方式下载到Spartan-3E 的32 bit数据在块内是连续的,但是块与块之间是不连续的,为了保证FPGA 加载过程不中断,在Spartan-3E 中需要一个FIFO 将数据进行缓冲,从而保证BIT 数据流的连续性。为了确保

- 基于DSP的CPCI总线架构设计的实时图像信号处理平台(03-27)

- 一种CPCI总线结构微波接收机的设计方案(12-21)

- 一种基于CPCI总线的智能故障信息系统子站(12-20)

- PCI IP核在CPCI总线数据采集卡的应用设计(12-15)

- SOPC在PCI总线高速数据传输系统中设计应用(12-12)

- CPCI总线技术在加固计算机的开发平台中的应用(01-11)