一种CPCI总线结构微波接收机的设计方案

0 引言

微波接收机是一种重要的无线通信设备,随着车载、机载、舰载等移动环境下的应用需求的产生,微波接收机的小型化、模块化、通用化是当前必须解决的问题。

Compact PCI 简称CPCI,是目前科研和军工领域广泛应用的一种工业计算机总线标准。CPCI 结合了PCI 总线的电气、软件标准和欧式卡的工业组装技术标准,与PCI 规范完全兼容;定义了32 位数据总线 ( 可扩展到64 位),最高工作频率为 33MHz ;能够实现设备的即插即用;系统设计结构紧凑、可靠性高,适应各种运输、使用环境。

结合CPCI 总线技术的微波接收机性能优良,可以满足智能交通、航空航天等众多领域的应用要求。

1 系统原理

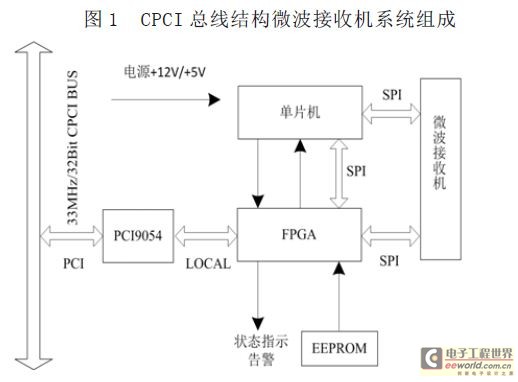

本接收机系统以FPGA 和单片机为中心控制单元,实现CPCI 总线结构下微波信号的接收、滤波、变频、增益控制等功能。系统主要由微波接收机、PCI9054、FPGA(EP1C6Q240C8)和单片机(Atmega8L)组成,系统组成如图1 所示。

CPCI 总线信号经高传输速率的PCI 桥芯片PCI9054 转换为LOCAL Bus 信号,通过Verilog HDL 语言编程产生对FPGA 的控制信号,完成数据的快速读写,同时在外部采用EEPROM 进行高速数据的缓冲,从而实现与FPGA 与CPCI 总线的高速数据通信。在控制信号作用下,FPGA 实时接收LOCALBus 信号,并进行运算处理,对接收机增益进行控制;对系统锁相环的控制指令、数据则通过串口发送给单片机,FPGA 和单片机共同完成对接收机系统的控制。系统供电由CPCI 机箱内5V、12V 开关电源提供。

2 关键技术设计

根据CPCI 总线规范及结构特点要求,CPCI 总线结构微波接收机系统的设计需要解决总线接口转换、结构设计、电源设计以及电磁兼容设计等关键技术。

2.1 总线接口转换

2.1.1 CPCI Bus 到LOCAL Bus 的接口设计

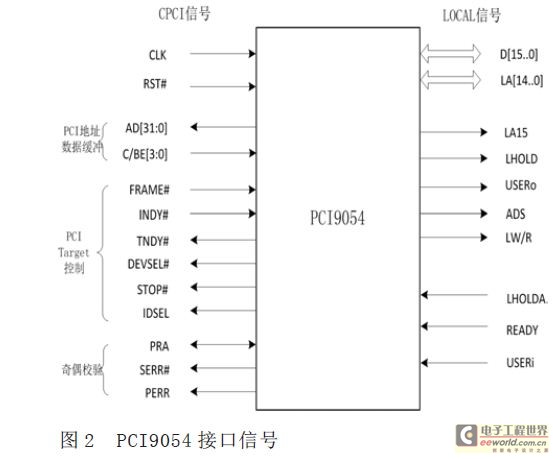

CPCI 总线信号到LOCAL 总线信号的转换是基于PCI9054芯片实现的。PCI9054 是PLX 公司生产的一款基于PCI2.2总线规范的通用接口芯片,是32 位、33MHZ的PCI总线主I/O 加速器,突发传输速度可达132MB/s.有M、J、C 三种工作模式,本设计中选用数据线与地址线独立使用的C 模式。

PCI9054 支持主控、目标、DMA( 直接存储器访问)3 种局部总线传输方式,这里采用了目标传输方式和高传输速率的DMA传输方式,即PCI9054 既是PCI 总线的目标,同时又是LOCAL总线的主控者。

PCI9054 提供了3 种物理总线接口:CPCI 总线接口、LOCAL 总线接口和串行EEPROM 接口,其中需要用户设计的是LOCAL 总线接口。其接口信号见图2.

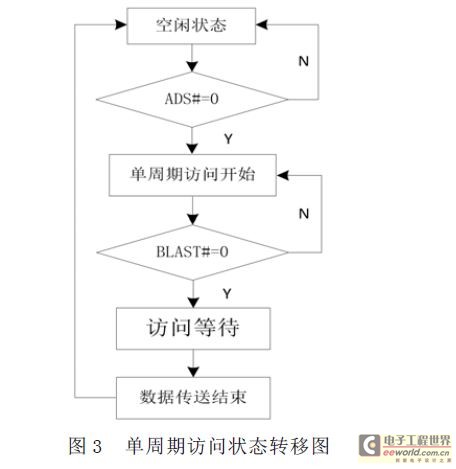

PCI9054 对本地设备的访问有单周期访问和突发方式访问2 种访问方式,单周期访问可采用状态机实现对LOCALBus 接口的控制,其状态转移如图3 所示。

2.1.2 SPI 总线接口设计

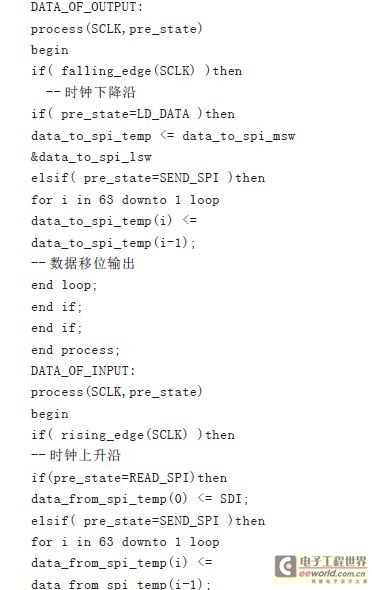

FPGA 与单片机的通信需要通过SPI 总线来实现。SPI总线是一种同步串行总线,以3 线或4 线方式通信。本设计中所使用的3 条通信线为:时钟SCLK,数据DAT,片选信号CS.图4 为SPI 工作时序。

当FPGA 从单片机读取数据时,向单片机发送读使能信号RD(可用任意I/O 口),串行数据经DAT 口在每个时钟(SCK)的上升沿送入FPGA 的移位寄存器,全部接受完毕后,CS 置1 ;当FPGA 向单片机传输命令或者数据时,CS 拉低后,移位寄存器开始工作。内部并行数据经串/ 并转换为64 位串行信号,每个时钟的下降沿移位寄存器送出一位数据,单片机通过DAT 端口读取数据。借助VHDL 硬件描述语言可方便地实现该系统,部分程序如下:

2.2 结构设计

微波接收机的全部硬件电路设计在一张CPCI 载板上,通过高密度2mm 插针式连接器安装在一个6U 标准机箱内。机箱采用220V 交流供电,前面板设有状态指示灯,可指示系统供电、PCI 总线访问状态及微波接收机内部射频模块锁定状态。

CPCI 总线结构的设计使该模块具有“即插即用”的高度兼容性,方便接收机系统的建立、操作,且具有良好的抗震性,适合移动平台的使用。

2.3 电源设计

由于CPCI 机箱提供的开关电源电磁干扰严重,且纹波系数较大,严重影响接收机杂散、相噪等性能,因此必须对电源进行处理。机箱内12V 开关电源经LM7809、LM7805、LT1965三级DC/DC 稳压后,分别提供给系统中数字电路、模拟电路使用,有效降低了电源纹波和数字电路、模拟电路之间的电磁干扰。

2.4 电磁兼容设计

CPCI 结构微波接收机的电磁干扰来源有机箱内部的电源干扰及接收机的本振频率泄露等。为了消除电源干扰的影响,将CPCI 机箱内计算机电源和接收机电源分开使用,并进行多级稳压处理;模块内敏感电路采用单独的屏蔽盒进行隔离,减少频率泄露;在PCB 板设计中将射频线和控制线分层隔离;为了减小载板上其他模块的信号对底

CPCI总线结构微波接收机的设计方 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)