LVDS已淘汰?LVDS和JESD204B将继续长期发展

前些年,LVDS(低压差分开关)开始逐渐取代CMOS。 而如今,JESD204B也显现出类似的发展趋势。

CMOS I/O接口包含单独的单端逻辑信号。 LVDS将这些单端逻辑信号转变为180°反相(从而是差分)信号线路对。 差分信号可产生更高的抗干扰能力,因此通常能够以更低功率水平工作,以实现等效信噪比。 JESD204接口标准针对通过串行链路发送和接收数据,通常是从ADC至FPGA或ASCI。 其它修订版本则阐述时钟和多个数据信号路径(“通道”)相关内容,以及通道同步问题。 显然,系统设计人员似乎不愿意对转换器与FPGA或ASIC之间的接口做出这么大的改变。 毕竟,这需要修改设计,不是吗? 人们理所当然地认为做出改变应该很容易。 纵观大局,改变需要进行工程设计,需要付出时间和金钱。 然而,随着技术的不断进步以及系统带宽要求越来越高,同样必须进一步提高转换器的采样速率。 这就使得LVDS将不再适用。 虽然LVDS的电流和功耗依然相对较为平坦,但接口的最高速度受到了限制。 这是由于驱动器架构以及许多数据线路都必须与某个数据时钟同步所导致的。

表1显示,当12位转换器以200 MSPS采样速率运行时,JESD204B使用的CML(电流模式逻辑)输出驱动器的功耗效率更具优势。 由于数据的串行化,与LVDS和CMOS驱动器相比,给定分辨率下CML所需的输出对数较少。 表中数据假设CMOS和LVDS输出的每个通道均采用同步时钟,使用CML输出时JESD204B的最大数据速率为4.0 GB(比JESD204B限值12.5 GB的一半还低)。 使用JESD204B时,引脚数量明显减少。

表1

引脚数量比较 – 200MSPS转换器

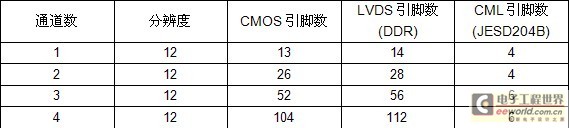

借此,对以2.0GSPS采样速率运行的12位转换器进行进一步的讨论。 通过表2,我们能够更加清楚地看到使用JESD204B的好处。 因为使用CMOS输出与千兆采样转换器接口完全不可行,所以本例中我们将不考虑CMOS。 在这种情况下,我们将转换器通道数量限制为四通道。 为确保数据速率处于当今市场上大多数FPGA的限值范围内,每位需要两对LVDS输出。 如表中所示,由于采用JESD204B减少了输出引脚的数量,所以明显降低了输出路由的复杂性。

表2

引脚数量比较 – 2.0GSPS转换器

综上所述,LVDS并不会被完全淘汰。 因为MSPS系列转换器仍拥有较大的市场。但是,LVDS需注意的是,JESD204B的时代即将到来!

淘汰继续长期发 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)